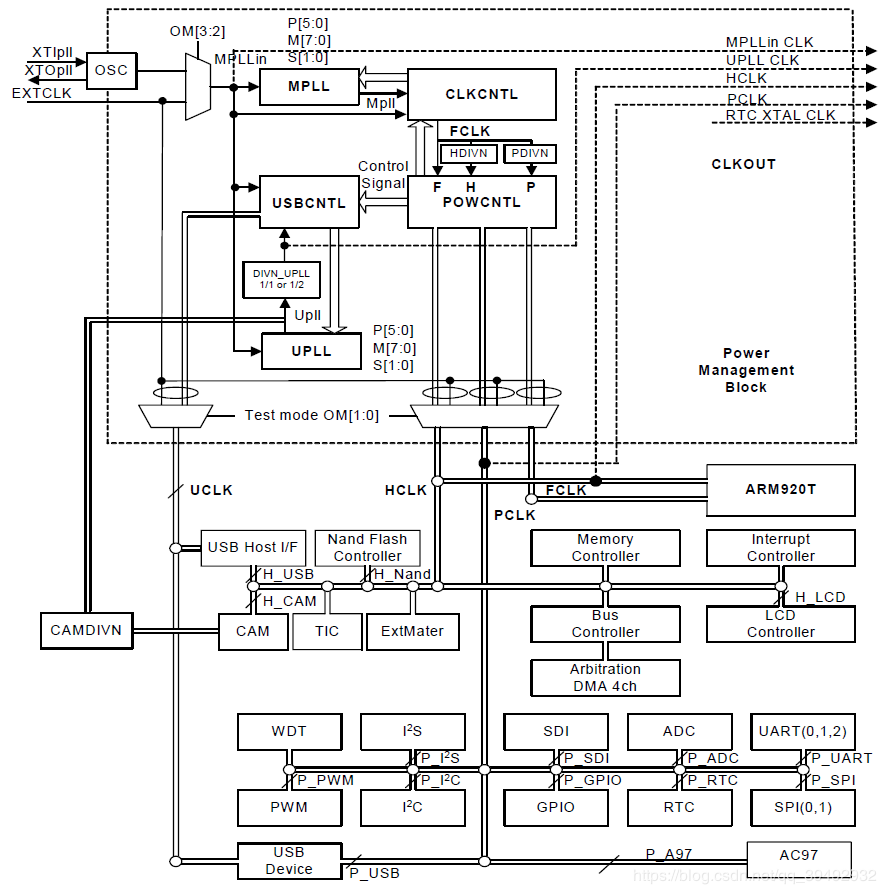

由時鐘樹分析,時鐘源通過選擇器接入給MPLL(Main PLL)與UPLL(USB PLL)

經過MPLL得到FCLK提供給CPU[ARM920T]

FCLK分別通過HDIVN與PDIVN分頻得到HCLK與PCLK

HCLK接入給AHB總線,再給各種高速設備(Nand Flash、內存控制器、中斷控制器…)

PCLK接入給APB總線,再給各種低速設別(I2C、PWM、GPIO、UART…)

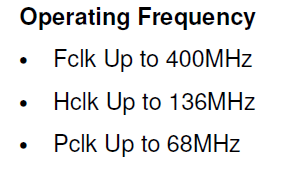

1.時鐘源最大值

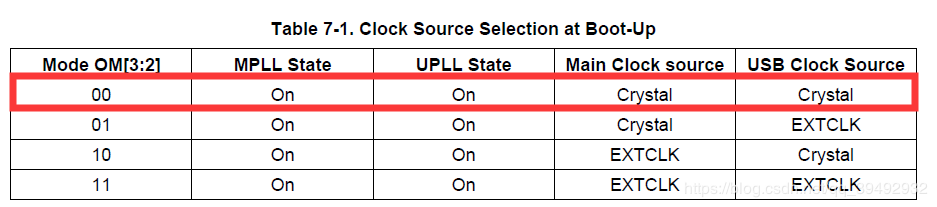

2.時鐘源

2.1 兩種時鐘源

1.晶振

2.外部引腳時鐘輸入

2.2 選擇時鐘源

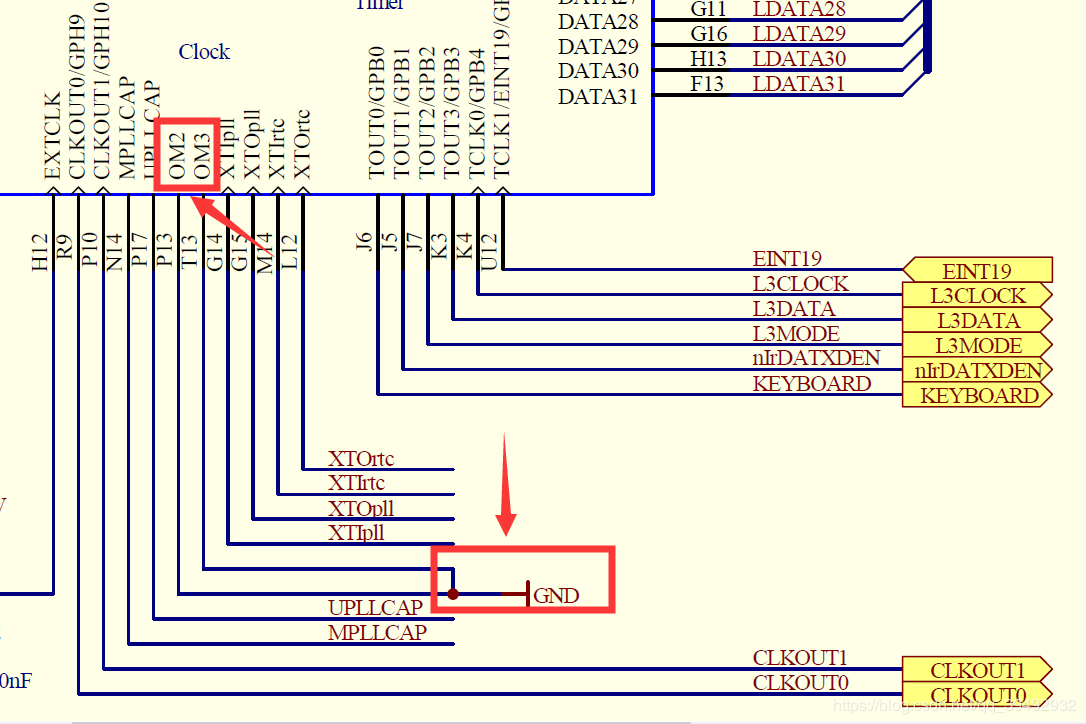

通過改變OM[3:2]引腳來選擇時鐘源

JZ2440 OM[3:2]接入GND,則主時鐘源與USB時鐘源都選擇外部晶振

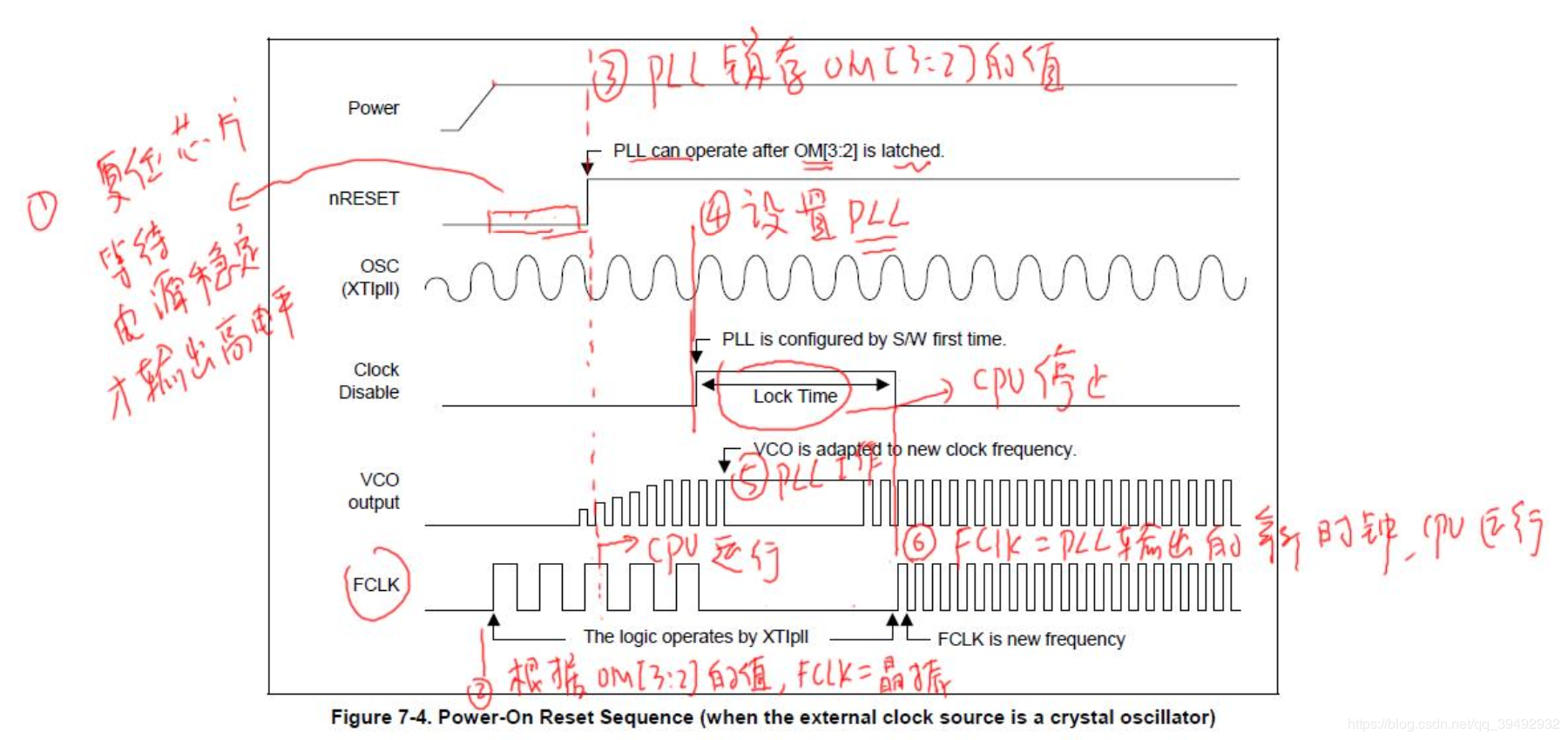

3.上電時鐘分析

復位等待, 等待電源穩定,復位芯片才輸出高電平

2.根據OM[3:2]的值,FCLK=晶振

3.PLL鎖存OM[3:2]的值

4.設置PLL(Lock Time中 CPU停止)

5.PLL工作

6.FCLK=PLL輸出新的時鐘,CPU運行

4.編程控制時鐘速度

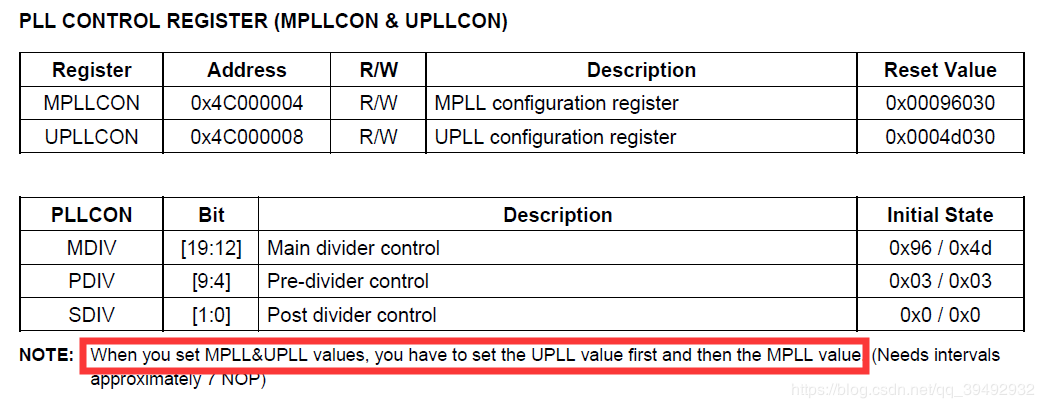

主要通過設置MPLLCON與CLKDIVN兩個寄存器來控制時鐘速度

外設時鐘使能寄存器CLKCON,可以使得功耗更低(低功耗)

編程目標:FCLK=400MHz、HCLK=100MHz、PCLK=50MHz

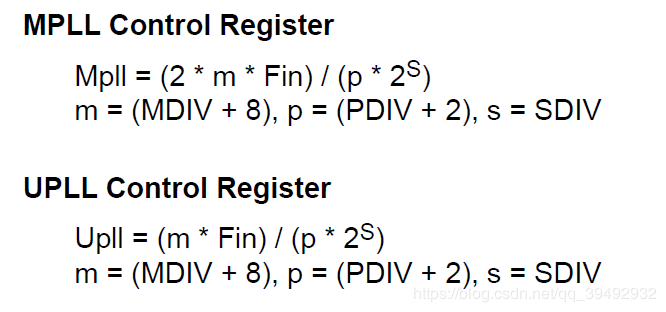

4.1 時鐘計算公式

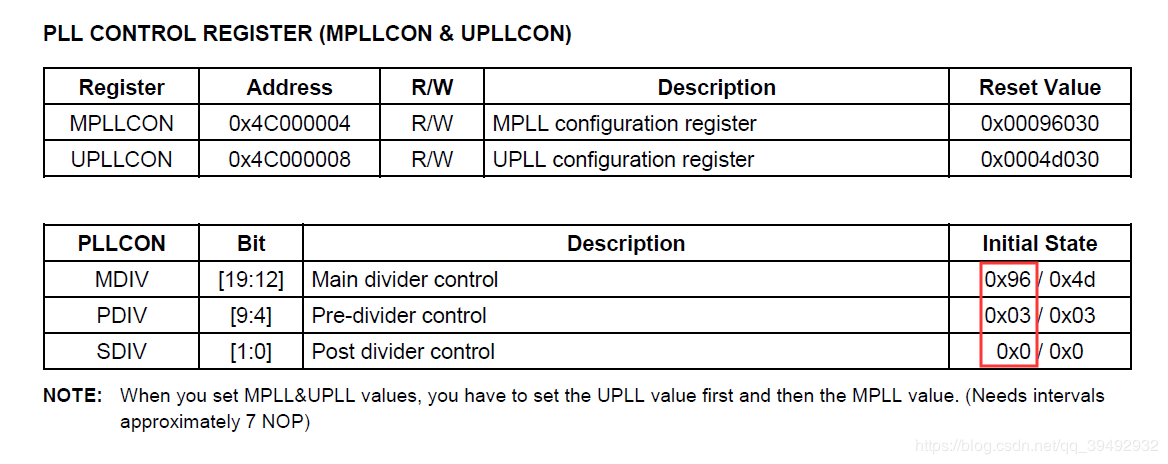

4.2 MPLLCON寄存器

PDIV=1,SDIV=1,由公式可得MDIV=92

/* 設置MPLLCON(0x4C000004) = (92<<12) | (1<<4) | (1<<0)

* m = MDIV+8 = 92+8 =100

* p = PDIV+2 = 1+2 =3

* s = SDIV = 1

* FLCK = (2*m*Fin)/(p*(2^s)) = (2*100*12M)/(3*2^1) = 400M

*/

ldr r0, =0x4C000004

ldr r1, =(92<<12) | (1<<4) | (1<<0)

str r1,[r0]

//一旦設置PLL,就會鎖定LOCK TIME直到PLL輸出穩定,然后CPU工作

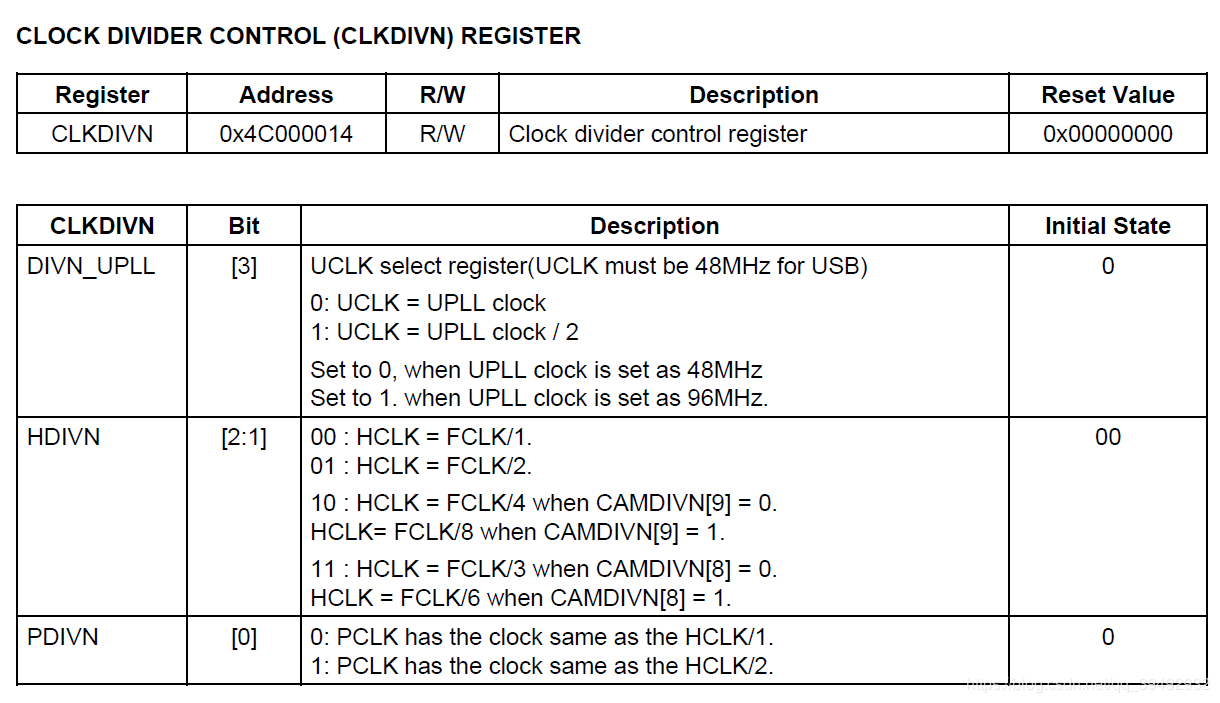

4.3 CLKDIVN寄存器

目標:FCLK=400M、FCLK=100M、PCLK=50M

則HDIVN設置為10(因為CAMDIVN默認值為0,所以無需關注),PDIVN設置為1

/* CLKDIVN(0x4C000014) = 0x05,fFCLK:fHCLK:fPCLK = 8:4:1 */

ldr r0, =0x4C000014

mov r1, #0x05

str r1,[r0]

5.注意事項

設置異步模式

如果HDIVN不是0,需要設置為異步模式,否則CPU會使用HCLK

#R1_nF:OR:R1_iA = 0xC0000000

5.1 注釋

MRC指令將協處理器的寄存器中數值傳送到ARM處理器的寄存器中

MCR指令將ARM處理器的寄存器中的數據傳送到協處理器的寄存器中

c:co-process 協處理器、r:寄存器

匯編版本

mrc p15,0,r0,c1,c0,0

orr r0,r0,#R1_nF:OR:R1_iA

mcr p15,0,r0,c1,c0,0

C版本

__asm{

mrc p15, 0, r1, c1, c0, 0 /* 讀取CP15 C1寄存器 */

orr r1, r1, #0xc0000000 /* 設置CPU總線模式 */

mcr p15, 0, r1, c1, c0, 0 /* 寫回CP15 C1寄存器 */

}

6.S3C2440默認時鐘頻率

由芯片手冊可知MPLLCON默認初始值為:

MDIV = 0x96 = 150

PDIV = 0x03

SDIV = 0

即:

m = MDIV+8 = 158

p = PDIV+2 = 5

s = SDIV = 0

可以推出:Fclk = (2 * m * Fin)/(p*(2^s)) = (2 * 158 * 12M)/(5 * 2^0) = 379.2M

上一篇:【ARM裸板】內存控制器、SDRAM基礎與代碼重定位

下一篇:【ARM裸板】啟動文件與棧的簡略分析

推薦閱讀

史海拾趣

隨著電子行業的快速發展,Catalyst公司不斷追求技術創新和突破。在某次關鍵的技術研發中,公司成功攻克了一項行業難題,推出了一款具有劃時代意義的新產品。這款產品不僅性能卓越,而且具有極高的性價比,迅速贏得了市場的廣泛認可。Catalyst憑借這一技術突破,成功引領了市場潮流,進一步鞏固了其在行業內的領先地位。

XXXX年,中國電子信息產業集團公司(CEC)和重慶臨空開發投資公司牽頭收購了Bridgelux。這次收購為Bridgelux帶來了強大的資本支持和市場資源,使其得以進一步擴大生產規模,提升研發能力。在CEC和重慶臨空的支持下,Bridgelux在全球范圍內的市場份額逐步提升,品牌影響力不斷增強。

2019年1月底,Entegris與Versum Materials宣布合并。合并后的公司由Entegris占據五席董事,而Versum占四席。Versum是一家主要生產半導體的化學、氣體及輸送系統的公司,兩家公司的前三大客戶均為臺積電、英特爾、三星電子。合并后,新公司在半導體材料市場的影響力顯著增強,同時也面臨著來自德國默克等競爭對手的挑戰。

隨著半導體材料開發成本的提高,產業鏈開始發生變革。Entegris通過與其他公司的合作與并購,積極適應這一變革。例如,與Versum Materials的合并就是Entegris在產業鏈變革中做出的重要決策之一。通過這一合并,Entegris能夠更好地整合資源,提升市場競爭力。

以上是關于Entegris公司在電子行業發展的5個故事概述。這些故事涵蓋了Entegris在合并、知識產權保護、技術創新、純度控制以及產業鏈變革等方面的關鍵事實。

隨著半導體材料開發成本的提高,產業鏈開始發生變革。Entegris通過與其他公司的合作與并購,積極適應這一變革。例如,與Versum Materials的合并就是Entegris在產業鏈變革中做出的重要決策之一。通過這一合并,Entegris能夠更好地整合資源,提升市場競爭力。

以上是關于Entegris公司在電子行業發展的5個故事概述。這些故事涵蓋了Entegris在合并、知識產權保護、技術創新、純度控制以及產業鏈變革等方面的關鍵事實。

|

先說明一點,希望有知道的給小弟一點建議,不知道的不要說,就說自己不清楚或者是知道一點,就行,這樣我能準確的判斷問題,不要擔心分值的問題,只要回復我就給分,24小時之內結貼,說到做到,看我的結帖率就知道了! 小弟想問一個問題,我想上北 ...… 查看全部問答∨ |

是這樣的,我做了打印機的驅動,然后在“畫筆”中打印,發現DrvEnablePDEV進去了,可是立馬又調用了DrvDisablePDEV,連DrvStartDoc都沒有進去,是不是因為沒有AddForm導致的,還會不會有其它的問題導致這種現象?我非常渴望大家的意見。… 查看全部問答∨ |

|

430做的保護器,可以控制SIM300模塊發送接收短信,現在有的問題,當設備運行久了,就會出現死機,或不響應命令即不接收短信,剛開始一切正常,過差不多一天多點就出現問題了,請高人指點… 查看全部問答∨ |

由于POV特殊的自身特點,象素點不是點陣式排列的,用普通點陣,LCD取模軟件會造成顯示內容是外大內小,成扇形的,所以這個軟件取出的數據克服這一特點。下一步我將準備脫離這個軟件,用控制芯片實現解碼 哈哈 關注的人錯過88 我 ...… 查看全部問答∨ |

|

周立功的tcp/ip代碼里的hardware.c里rec_packet函數里有這么一段 if(bnry!=curr) //此時表示有新的數據包在緩沖區里 { //在任何操作都最好返回page0 if(REC_BUFF_NUM==MAX_REC_BUFF)//接收緩沖區號清零 { REC_BUFF_NUM=0; } REC_BUFF_PTR_WO ...… 查看全部問答∨ |

我用的是4系列的,問個關于內部RTC寫入的問題。 當RTC配置好啟動后。如果用戶需要通過按鍵修改時間的話,修改RTCHOUR和RTCMIN的時候,需要事先關閉RTC模塊嗎?還是直接改寫就可以呢?怎樣做是安全的,不會出錯的? 430的內部RTC還有什么其它的注 ...… 查看全部問答∨ |

DF75435

DF75435

京公網安備 11010802033920號

京公網安備 11010802033920號