有些朋友不理解為什么STM32時鐘要先倍頻N倍,再分頻?你會擔心這個值太大嗎?

1寫在前面

STM32時鐘的功能,可以說是越來越強大了。

從各個系列的時鐘樹可以看得出來,最早F1系列的時鐘功能相對比較簡單,到這后面H7、G0的時鐘越來越豐富。

今天講述一下其中的PLL環節。

2關于PLL

什么是PLL?

PLL:Phase Locked Loop鎖相環。

PLL用于振蕩器中的反饋技術,通常需要外部的輸入信號與內部的振蕩信號同步。

一般的晶振由于工藝與成本原因,做不到很高的頻率,而在需要高頻應用時,由相應的器件VCO,實現轉成高頻,但并不穩定,故利用鎖相環路就可以實現穩定且高頻的時鐘信號。

每一塊STM32處理器至少都有一個PLL,有的甚至有好幾個PLL。

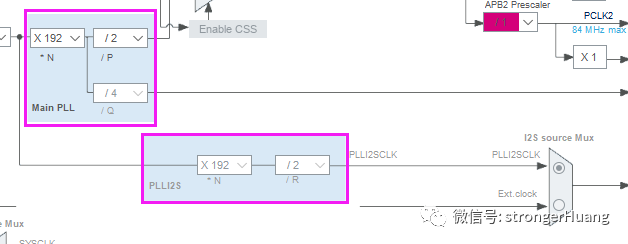

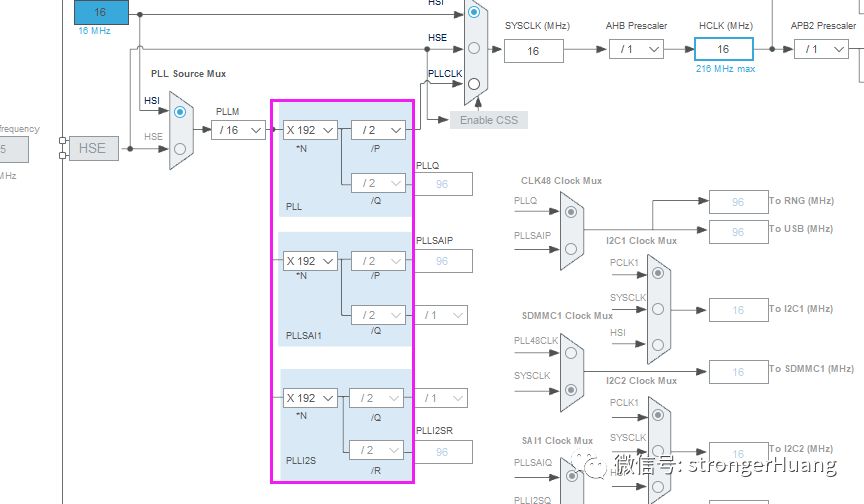

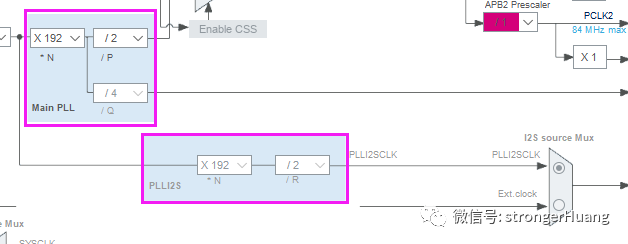

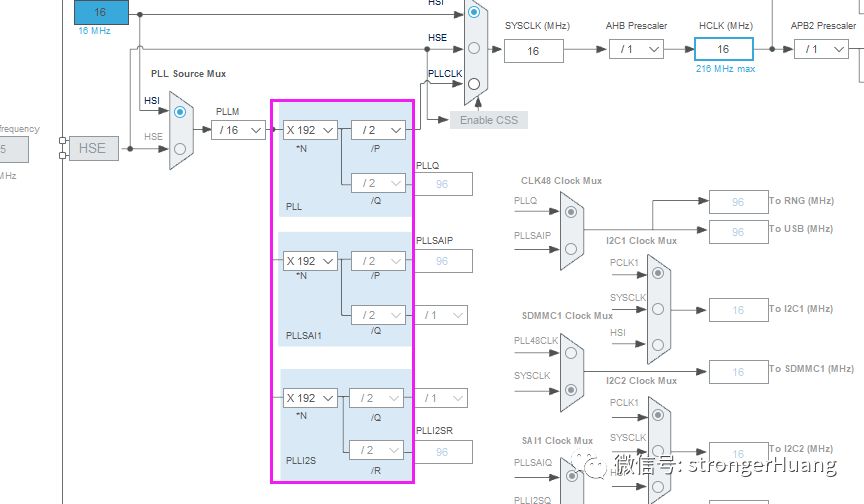

比如,F4有兩個PLL:

F7有三個PLL:

當然,每個MCU型號不同,其PLL數量,及功能也有差異,具體需要看相應手冊。

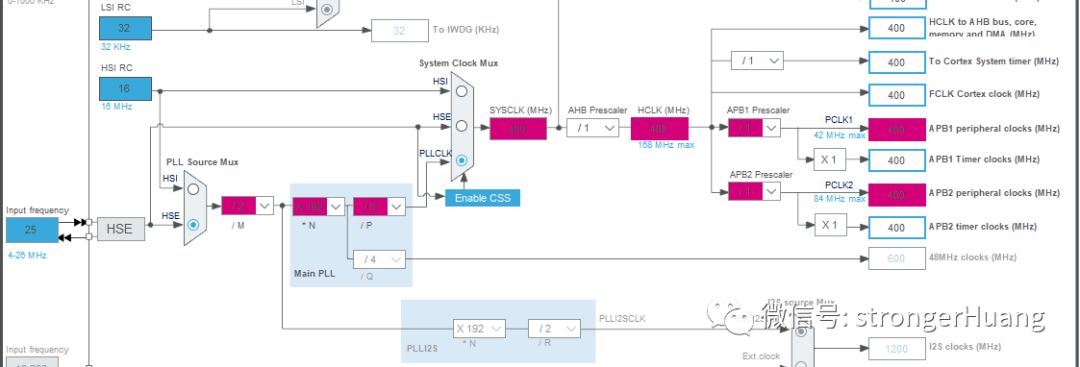

3STM32CubeMX配置時鐘樹

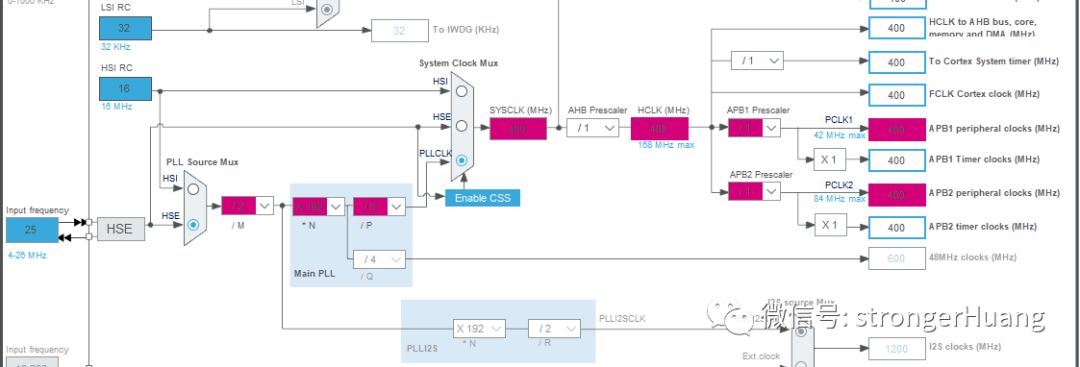

STM32CubeMX配置時鐘不用擔心出錯。

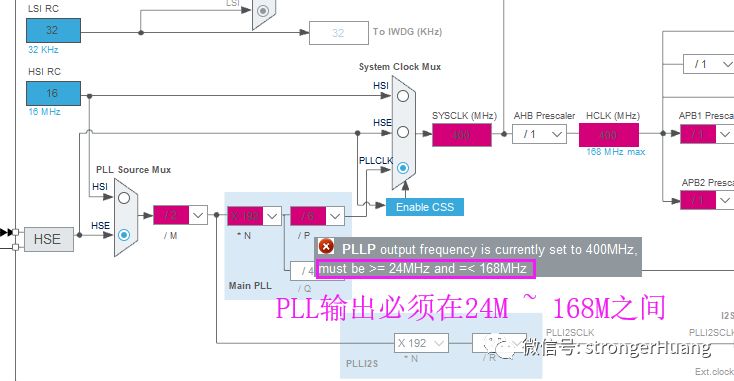

原因很簡單,這個工具配置時鐘樹,如果出錯,會有紅色警告。

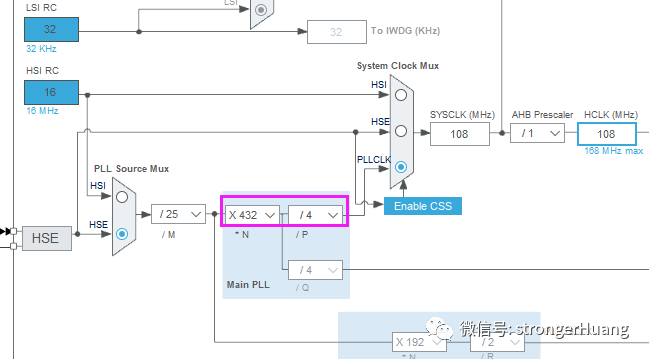

如下圖:

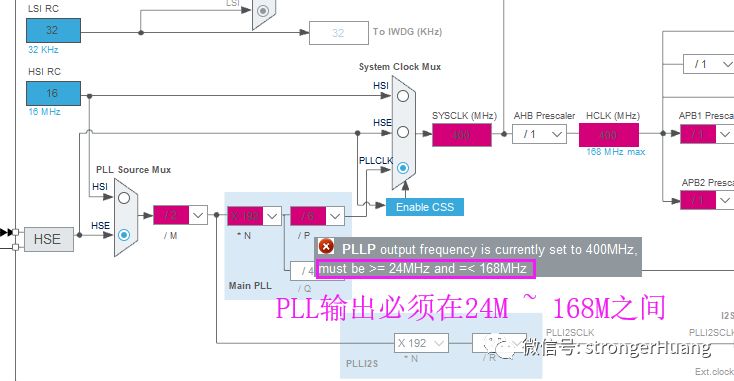

具體每一個紅色警告錯誤的原因,將光標移到紅色警告過會有相應提示信息。

比如,輸出PLLP值超過規定范圍:

有這個提示信息,再也不怕配置出錯了。

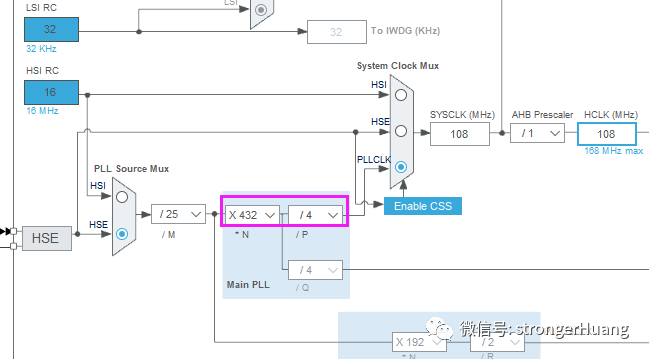

PLL的倍頻和分頻值

有人覺得前面倍頻N值很大(如下圖),這樣會不會出問題?

答案肯定是不會。但不建議將參數N設置為最大值。

特定時鐘頻率

有些時候,我們要求有特定時鐘頻率,比如USB,ETH等。這個時候PLL參數就需要合理才行。

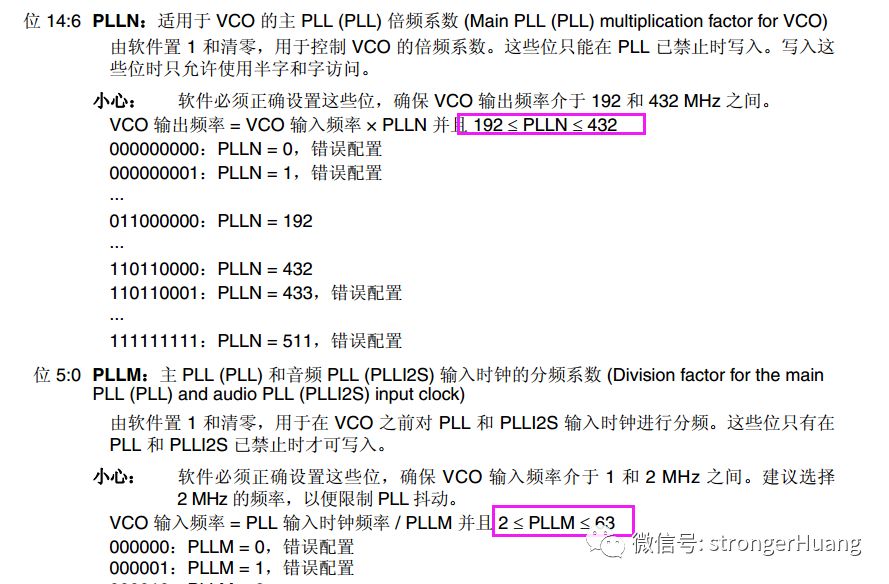

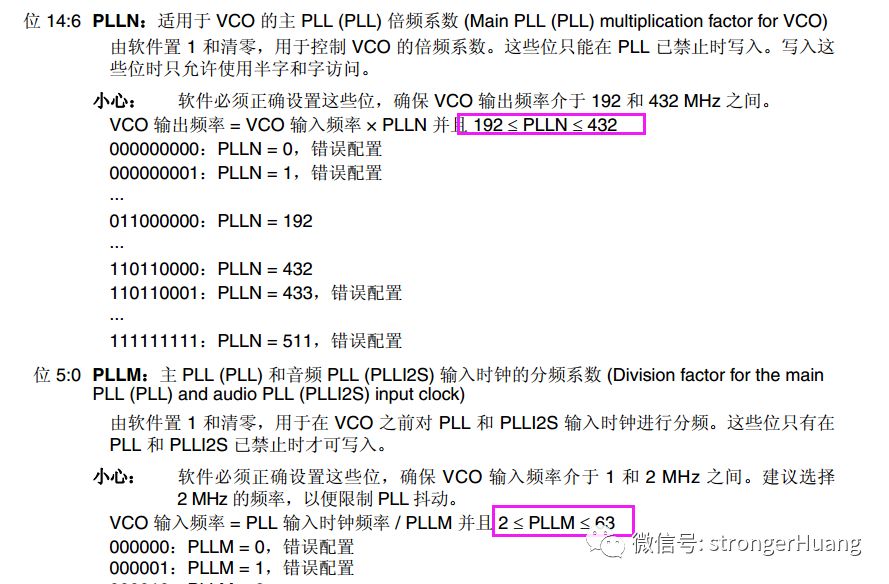

4STM32手冊可查看PLL參數范圍

STM32的時鐘,在之前使用標準庫,或者寄存器時,使用的晶振頻率不是官方推薦的,很多人就會搞暈。

那么,就只有參看對應手冊,手冊上是有明確說明的。比如F4手冊RCC章節,詳細說明的PLL各參數值范圍。

關鍵字:STM32 時鐘 倍頻 分頻

引用地址:

STM32時鐘要先倍頻N倍再分頻的原因是什么?

推薦閱讀最新更新時間:2025-05-04 21:13

高手帶你理解STM32系統時鐘和分頻

首先來手冊里的一段話。 三種不同的時鐘源可被用來驅動系統時鐘 (SYSCLK) · HSI振蕩器時鐘 · HSE振蕩器時鐘 · PLL時鐘 一般用的是PLL時鐘,后面有證據。 我們可以通過庫函數獲取各時鐘值 void RCC_GetClocksFreq(RCC_ClocksTypeDef* RCC_Clocks) 在我的系統里,把時鐘值打印信息如下: SYSCLK:0x44aa200 //72000000, 72MHz HCLK:0x44aa200 //72000000, 72MHz PCLK1:0x2255100 //36000000, 36MHz PCLK2:0x44aa200 //7200

[單片機]

ATtiny13 系統時鐘預分頻器

ATtiny13 系統時鐘可通過設置時鐘預分頻寄存器 CLKPR 來分頻。該特性可用來降低功 耗。該分頻器對所有時鐘源都有效,且可影響 CPU 時鐘頻率及所有同步外設。 clkI/O、 clkADC、clkCPU 及clkFLASH 分頻因子見Table 9 。 時鐘預分頻寄存器-CLKPR · Bits 7 – CLKPCE: 時鐘預分頻器變化使能 CLKPCE 位必須置 1”使能 CLKPS位。只有當CLKPR寄存器的其他位同時寫 0”時, CLK- PCE位改變。CLKPCE在寫入四個周期后或當CLKPS位寫入后由硬件清零。在暫停周期 中重新寫 CLKPCE 位,既不擴展暫停周期,也不清除 CLKPCE 位。 · Bit

[單片機]

淺析AD9522時鐘分頻電路原理

在集成度高度發展的今天,不能靠多個晶振源來解決問題,而且一旦晶振固定那么它的靈活性和可移植性必然受到很大影響,所以一些時鐘分頻芯片應運而生,今天我們將舉一個很有代表性的AD9522時鐘分頻芯片的典型應用來達到一個拋磚引玉的作用。 一、AD9522簡介 1.外部特性 A D 9 5 2 2是一個多路時鐘輸出和分配功能的芯片,本身支持亞皮秒抖動性能,在芯片內部還集成了PLL(PhaseLockedLoop)和VCO(壓控振蕩器)。VCO的調諧范圍是 2.02GHz~2.335 GHz.AD9522串行接口支持SPI與I2C的數據總線,芯片內部的EEPROM可通過串口進行編程,可以用來存儲用戶配置的寄存器數據從而使輸入時鐘分頻。AD95

[電源管理]

STM32入門-時鐘篇

STM32中使用任何一個外設都必須打開相應的時鐘。在STM32中有5個時鐘源可供用戶選擇: 1.HSI高速內部時鐘,RC震蕩器,頻率為8MHz。 2.HSE高速外部時鐘,右英/陶瓷諧振器,或著外部時鐘源,4MHz-16MHz. 3.LSI內部低速時鐘,RC震蕩器頻率為40Hz。 4.LSE外部低速時鐘,接頻率為32.768KHz的石英晶體。 5.PLL鎖相環頻輸出,時鐘源可選為HIS/2、HSE或HSE/2。倍頻可選2-16倍,但其輸出頻率最大不能超過72MHz。 系統時鐘SYSCLK,它是供STM32中絕大部分器件工作的時鐘源,系統時鐘可選擇為PLL輸出、HSI或者HSE。系統時鐘的做大頻率為72MHz,它通過AHB分頻器分頻后

[單片機]

不可錯過的單片機STM32的5個時鐘源知識

眾所周知STM32有5個時鐘源HSI、HSE、LSI、LSE、PLL,其實他只有四個,因為從上圖中可以看到PLL都是由HSI或HSE提供的。 其中,高速時鐘(HSE和HSI)提供給芯片主體的主時鐘.低速時鐘(LSE和LSI)只是提供給芯片中的RTC(實時時鐘)及獨立看門狗使用,圖中可以看出高速時鐘也可以提供給RTC。 內部時鐘是在芯片內部RC振蕩器產生的,起振較快,所以時鐘在芯片剛上電的時候,默認使用內部高速時鐘。而外部時鐘信號是由外部的晶振輸入的,在精度和穩定性上都有很大優勢,所以上電之后我們再通過軟件配置,轉而采用外部時鐘信號. 高速外部時鐘(HSE):以外部晶振作時鐘源,晶振頻率可取范圍為4~16MHz

[單片機]

STM32高級定時器之時鐘源

1、定時器時鐘源框圖 從圖片中可以看到定時器有4個時鐘源, (1)內部時鐘 ;(2) 外部時鐘模式1,定時器的通道1、2 ; (3) 外部時鐘模式模式2 ,ETR腳 ; (4)內部觸發輸入 下面分別介紹這幾種時鐘源的詳細配置 2、內部時鐘 寄存器SMCR的SMS選擇000 3、外部時鐘模式1 中文手冊已經有以通道2為例子詳細說明,這里我以通道1來說明,算是對它的溫故和補充 3.1 濾波器設置,我的理解這里的濾波,比如我這里配置為0001,不是說通道來了N=2個脈沖才算這個輸入有效,而是脈沖到來后,延時N/Fsampling的時間,還是高電平,就認為這個脈沖有效 類似按鍵檢測的延時去抖動,如果理解

[單片機]

STM32單片機上電后時鐘的默認配置過程

寫作原由:今日接手用stm32f100xx芯片開發的項目,以前用的是stm8s 和stm32f103xx芯片;因為在別人的項目代碼的基礎上做2次開發,但是發現那個代碼main函數中沒有對系統時鐘的設置的相關函數,一直納悶,但也沒有深究,直至昨日 調試時出現串口收發數據出錯,源代碼在原項目的板子上串口發送、接收數據正常,同樣程序在項目板子上收發的數據不正確, 兩塊板子芯片一樣,串口收發管腳一樣,最后發現原來板子外部晶振是8MHZ ,新板子外部晶振是12MHZ; 而在STM32固件庫中,默認的外部晶振是8MHZ,由于時鐘源不正確,導致波特率不正確,當然收發的數據也不正確了…..我勒個去!都怪自己平時看問題“不求甚解”。 波特率與時

[單片機]

STM32系統時鐘硬件仿真查看

前幾天回校調試基于407的程序,以前都是在別人的程序基礎上面改寫只要能實現想要的功能不會管其他的,結果基本就沒用用過硬件JLINK的硬件仿真,那晚蔡師姐幫忙一直弄到夜里12點多,真的很感謝她 后來師姐幫我發現那塊板子的系統時鐘不是原以為的時鐘168MHZ。后來用107程序查看了下發現那種查看系統時鐘的方法是可行的,今晚我用103也查看了下系統時鐘也是所想象的72MHZ. 閑話少說,下面粘上一個簡單查看當前單片機系統時鐘的小技巧,希望得到更多指引 1.在主程序里面的最前面假如下面倆行代碼: int main(void) { RCC_ClocksTypeDef RCC_Clocks; RCC

[單片機]

WeActStudio的STM32G431CoreBoard開發資料

WeActStudio的STM32G431CoreBoard開發資料 Keil.STM32F4xx_DFP2.13.0.pack

Keil.STM32F4xx_DFP2.13.0.pack PID控制器的結構及穩定性分析

PID控制器的結構及穩定性分析 OP06GY

OP06GY

京公網安備 11010802033920號

京公網安備 11010802033920號