一些晶圓代工廠仍在基于下一代全能柵極晶體管開發新工藝,包括更先進的高遷移率版本,但是將這些技術投入生產將是困難且昂貴的。英特爾、三星、臺積電和其他公司正在為從今天的FinFET晶體管向3nm和2nm節點的新型全柵場效應晶體管(GAA FET)過渡奠定基礎,這種過渡將從明年或2023年開始。

GAA FET將被用于3nm以下,擁有更好的性能,更低的功耗和更低的漏電壓。雖然GAA FET晶體管被認為是FinFET的演進,并且已經進行了多年研發,但任何新型晶體管或材料對于芯片行業來說都是巨大的工程。芯片制造商一直在盡可能長地推遲這一行動,但是為了繼續微縮晶體管,需要GAA FET。

需要指出的是,雖然同為納米片FET,但GAA架構有幾種類型。基本上,納米片FET的側面是FinFET,柵極包裹著它,能夠以較低的功率實現更高的性能。

圖1:平面晶體管與FinFET以及GAA FET,來源:Lam Research

“GAA技術對于晶體管的持續微縮至關重要。3nm GAA的關鍵特性是閾值電壓可以為0.3V。與3nm FinFET相比,這能夠以更低的待機功耗實現更好的開關效果,” IBS首席執行官Handel Jones說。“ 3nm GAA的產品設計成本與3nm FinFET不會有顯著差異。但GAA的IP認證將是3nm FinFET成本的1.5倍。”

轉向任何新的晶體管技術都具有挑戰性,納米片FET的推出時間表因晶圓廠而異。例如,三星正在量產基于FinFET的7nm和5nm工藝,并計劃在2022到2023年間推出3nm的納米片。同時,臺積電將把FinFET擴展到3nm,同時將在2024/2025年遷移到2nm的納米片FET。英特爾和其他公司也在研究納米片。

納米片FET包含多個組件,包括一個溝道,該溝道允許電子流過晶體管。首款納米片FET采用傳統的基于硅的溝道材料,但下一代版本將可能包含高遷移率溝道材料,使電子能夠在溝道中更快地移動,提高器件的性能。

高遷移率溝道并不是新事物,已經在晶體管中使用了多年。但是這些材料給納米片帶來了集成方面的挑戰,供應商正在采取不同的方法解決:

在IEDM(國際電子元件會議)上,英特爾發表了一篇有關應變硅鍺(SiGe)溝道材料的納米片pMOS器件的論文。英特爾使用所謂的“溝道優先”流程開發該器件。

IBM正在使用不同的后溝道工藝開發類似的SiGe納米片。

其他溝道材料正在研發中。

芯片微縮的挑戰

隨著工藝的發展,有能力制造先進節點芯片的公司數量在不斷減少。其中一個關鍵的原因是新節點的成本卻越來越高,臺積電最先進的300mm晶圓廠耗資200億美元。

幾十年來,IC行業一直遵循摩爾定律,也就是每18至24個月將晶體管密度翻倍,以便在芯片上增加更多功能。但是,隨著新節點成本的增加,節奏已經放慢。最初是在20nm節點,當時平面晶體管的性能已經發揮到極致,需要用FinFET代替,隨著GAA FET的引入,摩爾定律可能會進一步放慢速度。

FinFET極大地幫助了22nm和16/14nm節點改善漏電流。“與平面晶體管相比,鰭片通過柵極在三側接觸,可以更好地控制鰭片中形成的溝道,” Lam Research大學項目負責人Nerissa Draeger說。

在7nm以下,靜態功耗再次成為嚴重的問題,功耗和性能優勢也開始減少。過去,芯片制造商可以預期晶體管規格微縮為70%,在相同功率下性能提高40%,面積減少50%。現在,性能的提升在15- 20%的范圍,就需要更復雜的流程,新材料和不一樣的制造設備。

為了降低成本,芯片制造商已經開始部署比過去更加異構的新架構,并且他們對于在最新的工藝節點上制造的芯片變得越來越挑剔。并非所有芯片都需要FinFET,模擬、RF和其它器件只需要更成熟的工藝,并且仍然有很旺盛的需求。

但數字邏輯芯片仍在繼續演進,3nm及以下的晶體管結構仍在研發。最大的問題是,有多少公司將繼續為不斷縮小的晶體管研發提供資金,以及如何將這些先進節點芯片與更成熟的工藝集成到同一封裝或系統中,以及最終效果如何。

UMC業務發展副總裁Walter Ng表示:“這實際上是晶圓經濟。在尖端節點,晶圓成本是天文數字,因此,很少有客戶和應用能夠負擔得起昂貴的成本。即使對于負擔得起成本的客戶,他們的某些晶圓尺寸已經超過掩模版最大尺寸,這顯然會帶來產量挑戰。”

成熟節點和先進節點的需求都很大。D2S首席執行官Aki Fujimura表示:“芯片行業出現了分歧,超級計算需求(包括深度學習和其他應用)需要3nm,2nm等先進制程。與此同時,物聯網和其他量大、低成本的應用將繼續使用成熟工藝。”

為什么使用納米片?

最前沿的工藝有幾個障礙需要克服。當鰭片寬度達到5nm(也就是3nm節點)時,FinFET也就接近其物理極限。FinFET的接觸間距(CPP)達到了約45nm的極限,金屬節距為22nm。CPP是從一個晶體管的柵極觸點到相鄰晶體管柵極觸點間的距離。

一旦FinFET達到極限,芯片制造商將遷移到3nm / 2nm甚至更高的納米片FET。當然,FinFET仍然適用于16nm / 14nm至3nm的芯片,平面晶體管仍然是22nm及以上的主流技術。

全方位柵極不同于FinFET。Lam的Draeger解釋說:“全能門或GAA晶體管是一種經過改進的晶體管結構,其中柵極從各個側面接觸溝道并實現進一步微縮。早期的GAA設備將使用垂直堆疊的納米片。它們由單獨的水平板構成,四周均由門材料包圍。相對于FinFET,提供了改進的溝道控制。”

在納米片FET中,每個小片都構成一個溝道。第一代納米片FET的pFET和nFET器件都將是硅基溝道材料。第二代納米片很可能將使用高遷移率的材料用于pFET,而nFET將繼續使用硅。

納米片FET由兩片或更多片組成。最近,Letti展示了具有7片的納米FET。Leti的高級集成工程師Sylvain Barraud在論文中說,7片的GAA與通常的2級堆疊納米板GAA晶體管相比,具有3倍的性能改進。

從表面上看,3nm FinFET和納米片相比的微縮優勢似乎很小。最初,納米片FET可能具有44nm CPP,柵極長度為12nm。

但是,納米片相比FinFET具有許多優勢。使用FinFET,器件的寬度是確定的。但是,使用納米片,IC供應商有能力改變晶體管中片的寬度。例如,具有更寬的片的納米片提供更高的驅動電流和性能。窄的納米片具有較小的驅動電流,占用的面積也較小。

Imec CMOS技術高級副總裁Sri Samavedam說:“ GAA架構進一步改善了縮小柵極長度的短溝道控制,而堆疊的納米片則提高了單位面積的驅動強度。”

除了技術優勢外,代工廠也在開發納米片FET,這讓客戶選擇面臨困難。

按照現在的情況,三星計劃在2022/2023年間推出全球首個3nm的納米片。“風險試產有50%的概率在2022年第四季度。大批量生產的時間有60%的概率在2023年Q2至Q3。” IBS的瓊斯說。

使用新晶體管會帶來一些成本和上市時間風險。考慮到這一點,客戶還有其他選擇。例如,臺積電計劃將FinFET擴展到3nm,然后再使用納米片。

瓊斯說:“三星顯然是3nm GAA的領先者,但臺積電也在開發2024至2025年投產的的2nm GAA。TSMC有出色的營銷技巧,吸引了許多大型客戶使用其3nm FinFET技術。”

無論如何,開發5nm / 3nm及更先進制程芯片的成本是天文數字。因此,客戶正在尋找替代方案,例如先進封裝。

“隨著芯片尺寸的縮小,越來越難以在新節點上使用更小的晶體管,重點已轉移,比如先進封裝可以獲得更低的功耗,更高速度。” CyberOptics總裁兼首席執行官Subodh Kulkarni 。

納米片的制造

未來,領先的IC供應商將遷移到諸如納米片之類的GAA架構,這將面臨諸多挑戰。

“就像從平面到FinFET的過渡一樣,從FinFET到GAA的過渡也將是艱難的。” Lam Research計算產品副總裁David Fried說。“轉向FinFET時,最大的挑戰是優化垂直側壁上的器件,因此出現了許多表面處理和沉積挑戰。現在,使用GAA必須在結構底層優化設備。表面處理和沉會變得更具挑戰性。”

蝕刻,一種去除晶體管結構中材料的工藝,如今也更具有挑戰性。Fried說:“使用平面結構時,通常很清楚何時需要各向同性(共形)的過程而不是各向異性(定向)的過程。使用FinFET時變得有些棘手。使用GAA時,這個問題變得非常棘手。一些過程在某些地方需要各向同性,例如在納米線/片材下方進行蝕刻以及各向異性,這個過程極具挑戰。”

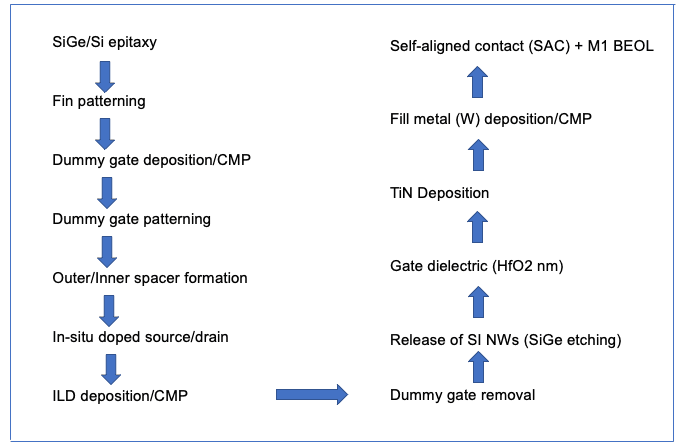

圖2:堆疊納米片FET的工藝流程。資料來源:Leti

在工藝流程中,納米片FET開始于在基板上形成超晶格結構。外延工具在襯底上沉積交替的SiGe和硅層。至少堆疊三層SiGe和三層硅組成。

下一步是在超晶格結構中制造微小的垂直鰭片。每個納米片彼此分開,并且在它們之間留有空間。在晶圓廠流程中,使用極紫外(EUV)光刻技術對鰭片進行構圖,然后進行蝕刻工藝。

Onto Innovation戰略產品營銷高級總監Scott Hoover表示:“ GAA晶體管的性能僅好于其最弱的溝道,因此需要單獨的納米片尺寸控制度量。通過超晶格形成鰭需要對厚度,成分和硅片CD進行單獨的層控制。”

然后是更困難的步驟之一——內部間隔物的形成。首先,使用橫向蝕刻工藝使超晶格結構中的SiGe層的外部凹陷。這樣會產生小空間,并充滿電介質材料。

TEL的技術人員羅伯特·克拉克(Robert Clark)表示:“由于不能停止蝕刻,控制內部間隔物凹槽蝕刻的工藝變化非常困難。理想情況下,只想在金屬的外延層穿過側壁間隔物的地方凹進去,然后用電介質內部間隔層替換該外延層。這是非常關鍵的5nm凹陷蝕刻,因為這是非線性且無法停止,難度相當于無網走鋼絲的過程。”

還有其他挑戰。“內部間隔模塊對于定義最終晶體管功能至關重要,對該模塊的控制對于最大程度地減少晶體管可變性至關重要。內部隔離模塊可控制有效柵極長度,并將柵極與源極/漏極epi隔離開。” KLA工藝控制解決方案總監Andrew Cross說道,“在該模塊中,SiGe會凹進去,然后內部隔離層會沉積并凹陷。在內部隔離物形成的每個步驟中,精確控制凹口和最終隔離物凹槽的形狀和CD對確保晶體管性能至關重要。而且,需要控制堆棧中每個單獨的溝道。”

接下來,形成源極/漏極,然后是溝道。這需要使用蝕刻工藝去除超晶格結構中的SiGe層,剩下的是構成溝道的硅基層或片。

“此步驟是GAA結構彼此分離,這可能導致具有挑戰性的缺陷,例如納米片之間的殘留物,納米片的損壞或與納米片本身相鄰的源/漏極的選擇性損壞。”Cross說。

挑戰不止如此。Onto's Hoover說:“形成溝道需要對板高、拐角腐蝕和溝道彎曲進行單獨控制。”

高k /金屬柵材料沉積在結構中,最后形成銅互連,從而形成納米片FET。“其他可能改變的模塊是設備的底部隔離和用于容納納米片的功能性金屬/層,但是這些模塊主要依賴于行業中已知/開發的工藝。

當然,即便不是全新的模塊,實現也變得越來越困難。

高遷移率器件

第一代納米片FET將是基于硅的溝道。這些納米片理論上優于FinFET,但并非總是如此。

“從FinFET到納米片,我們已經觀察到電子遷移率(對于nFET)有顯著的提高。問題將是pFET空穴遷移率下降。這就是我們需要解決的問題,” IBM設備與單元流程研發經理Nicolas Loubet在演講中說。

換句話說,芯片制造商需要提高納米片中的pFET性能。因此,供應商正在開發有改進的pFET第二代納米片FET。第二代納米片材將繼續提供基于硅的溝道用于nFET,因為它們能夠提供足夠的性能。

為了提高pFET,芯片制造商正在研究高遷移率溝道材料。更具優勢的材料是SiGe,而III-V族材料,鍺和其他材料也正在研發中。

英特爾設備工程師Ashish Agrawal在論文中說:“由于其優異的空穴遷移率,以及考慮到批量生產的成熟工藝,Strained SiGe最近成為有希望的pFET溝道來替代硅。”

為了加入這些材料,芯片制造商在晶圓廠中實施了所謂的應變工程工藝。應變是一種施加到硅上以改善電子遷移率的應力。

應變工程工藝并不新鮮,多年來,芯片制造商一直在溝道中使用SiGe合金應力以提高載流子遷移率。IBM高級研究員Shogo Mochizuki表示:“應變工程已成為CMOS技術的關鍵技術之一。從90nm節點開始,源極-漏極外延生長會在溝道中應變,有助于電子遷移。而且,在FinFET中仍然被使用。”

因此,芯片制造商自然會在下一代GAA晶體管中引入應變SiGe溝道材料,但有一些新的挑戰。

“我們建議用溝道SiGe代替溝道硅,這可以幫助增加移動性。此外,這項創新技術還幫助超低閾值器件獲得了卓越的可靠性,這是源漏外延基本應變技術無法提供的。” Mochizuki說。“使用新型溝道材料的納米片所面臨的最大挑戰是確保材料的均勻性和結構完整性,以及確保新型溝道材料與工藝兼容。”

最重要的是,有幾種方法可以開發SiGe pFET溝道,包括先形成溝道后形成溝道。

在IEDM上,英特爾發表了一篇關于在應變松弛緩沖器(SRB)上的SiGe納米片pMOS器件的論文。納米片溝道基于壓縮應變的SiGe和Si0.4Ge0.6的混合物。pMOS器件由5nm的片厚和25nm長的柵極組成。

溝道形成發生在常規納米片工藝的早期階段。從許多方面來說,這是SiGe溝道優先處理。

英特爾的工藝始于300mm基板,在基板上生長基于SiGe的SRB層。然后,在SRB層上生長壓縮Si0.4Ge0.6和拉伸硅的交替層。

這將創建一個超晶格結構,該結構構成pFET的SiGe溝道的基礎。英特爾公司的Agrawal說:“在這項工作中,我們展示了一個埋入式Si0.7Ge0.3 SRB整體應力源,可在Si0.4Ge0.6 pFET納米片中引起壓縮應變,從而增強了空穴傳輸。”

SRB的另一個術語是虛擬襯底。傳統上,硅襯底決定了沉積或生長在其頂部的所有外延層的晶格常數。

溝道和源極/漏極中應變的性質取決于該層相對于硅襯底之間的晶格常數的相對差異。Agrawal說,“對于SRB或虛擬襯底,我們通過在硅襯底頂部生長松弛的Si 0.7 Ge 0.3緩沖層來改變襯底本身的晶格常數。沉積在該緩沖層頂部的所有后續層將相對于Si 0.7 Ge 0.3應變。通過改變松弛Si 0.7形式的襯底晶格常數Ge 0.3緩沖液,我們可以實現應變納米片CMOS。”

其他公司則采取不同的方法。例如,在IEDM上,IBM發表了一篇用后形成溝道工藝在帶有應變SiGe溝道的納米片pFET的論文。

使用這種方法,IBM的pFET納米片峰值空穴遷移率提高了100%,相應的溝道電阻降低了40%,同時將次淋姐電壓值斜率保持在70mV / dec以下。

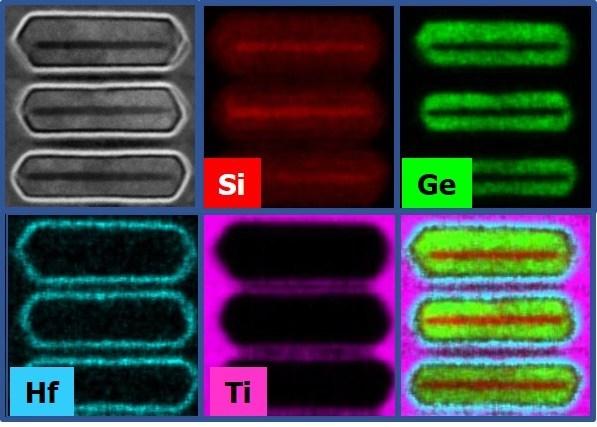

圖3:沿柵極柱M1外延生長4 nm厚的Si 0.65 Ge 0.35的堆疊SiGe NSs溝道的截面STEM圖像和EDX元素圖。Wsheet = 40nm。資料來源:IBM

IBM在流程的后半部分而不是在一開始就形成SiGe溝道。“我們意識到,在此過程的早期就開始進行SiGe生長外延對應變是無效的。這也給制造過程帶來了復雜性和成本。” IBM的Mochizuki說。“通過我們的新技術,SiGe層中的應變得以保留。發生這種情況的原因是此過程基于SiGe外延后向方案,對于提高性能至關重要。

更具體地說,IBM在溝道釋放過程之后開發SiGe溝道。溝道釋放后,水平和垂直修整硅納米片。然后,在修整后的硅納米片周圍選擇性包裹一個SiGe層,稱為SiGe覆層。 Mochizuki說,“最終的結構是帶有薄硅納米片芯的SiGe覆層。通過將載流子限制在SiGe覆蓋層內,可以在應變的SiGe溝道層中提高載流子遷移率。”

結論

GAA FET面臨幾個制造挑戰,而且成本非常高昂,以至于尚不清楚有多少芯片制造商能夠負擔得起。幸運的是,它不是唯一選擇。先進的封裝和新的架構肯定會在當前和未來的設備中發揮更大的作用。

沒有一種技術可以滿足所有需求。因此,至少就目前而言,這些都是選擇。

上一篇:歐菲光:成為攝像頭模組主流供應商

下一篇:今年科技股IPO漲幅較去年翻番 了市場泡沫顯現

推薦閱讀

史海拾趣

為了進一步提升市場競爭力,德欣公司開始在全球范圍內進行布局。公司先后在亞洲、歐洲、美洲等地設立了生產基地和研發中心,加強了與國際市場的聯系。同時,德欣公司還積極尋求與國際知名企業的合作,共同開發新產品、新技術和新市場。這些舉措不僅提升了德欣公司的品牌影響力和市場競爭力,也為其未來的發展提供了更廣闊的空間。

隨著技術的不斷進步和市場需求的增長,Dow-Key Microwave開始尋求技術突破和市場拓展。公司投入大量研發資金,加強與高校和研究機構的合作,成功開發出一系列高性能、高可靠性的射頻微波開關產品。這些產品廣泛應用于通信、航空、軍事等領域,贏得了客戶的廣泛贊譽。同時,公司還積極拓展國際市場,產品出口到多個國家和地區,進一步提升了公司的知名度和影響力。

全智景公司自成立以來,一直致力于電子視覺技術的研發。早期,公司面臨激烈的市場競爭和技術瓶頸,但全智景團隊憑借堅韌不拔的精神,成功研發出了一款具有劃時代意義的高清攝像頭芯片。這款芯片以其出色的圖像質量和穩定性,迅速獲得了市場的認可,并推動了整個電子視覺行業的進步。這一技術突破不僅讓全智景公司在市場上站穩了腳跟,也為公司后續的發展奠定了堅實的基礎。

ABI Electronics公司深知研發實力是企業發展的核心競爭力。因此,公司不斷加大對研發的投入,引進了一批高素質的研發人才,建立了完善的研發體系。通過與高校、科研機構等合作,ABI不斷吸收新的技術和知識,推動產品的升級換代,保持了在行業內的技術領先地位。

在競爭激烈的電子行業中,Davicom始終堅持自主研發,不斷突破核心技術。公司投入大量研發資金,建立了一支高素質的研發團隊,并申請了多項專利。通過多年的努力,Davicom在DSP IC及系統應用技術方面取得了重大突破,成功開發出多款具有競爭力的產品。

|

對小電流的測量非常微妙。巧妙的模擬設計技術、正確的器件和設備都有助于測量。 要 點 小電流的測量面臨物理限制與噪聲限制。 早期的機械電表可分辨毫微微安級電流。 JFET和CMOS放大器適用于測量。 要測量毫微微安級 ...… 查看全部問答∨ |

Stellaris,Beat STM32!!!血戰已拉開大幕 呵呵,這個口號我是替TI喊的。 想來TI的人心里應該也是這么想的。 TI收購Luminary之后一直很期待,原本市場上ARM Cortex-M3的基本上就是STM32一花獨放,這下可出來個對手了。 & ...… 查看全部問答∨ |

|

求220V輸入,12V/2A,5V/1A兩路輸出的開關電源圖 求220V輸入,12V/2A,5V/1A兩路輸出的開關電源圖,如果哪位兄弟有,請發一下,謝謝了。12V如果能到3A就更好了… 查看全部問答∨ |

|

|

我的Activesync能連接上WINCE,在移動設備中有顯示WINCE的內容,也能復制文件到WINCE,但是EVC不能與WINCE通信. 感覺很奇怪,不知道是什么原因引起的,大家指點一下了.搞了一天都沒有找到什么原因. 謝謝!… 查看全部問答∨ |

|

|

我用的是西門子6SE70變頻器,電壓為575,功率是700HP,變頻器帶兩個電機,現在有個電機的電纜破損了,把電纜用線鼻子連接使用。現在電纜承受的電流肯定受影響。現在要想設置一下變頻器的保護電流,如何設置。比如以前電流超過800A,變頻器就過流保護 ...… 查看全部問答∨ |

看不太懂enet-ptpd例程,怎么才能不8962評估板設置成slave——從時鐘模式? 把計算機設置成master——主時鐘模式? 以便計算機與8962評估板來對時?… 查看全部問答∨ |

M62392

M62392

京公網安備 11010802033920號

京公網安備 11010802033920號