簡介:介紹了基于Zynq平臺實現的JPEG圖像壓縮系統。該系統利用Zynq片上AXI總線實現了ARM與FPGA核間高吞吐率的數據交互操作,并結合了ARM和FPGA在嵌入式系統開發中各自的優勢,對軟硬件功能的實現進行了明確的劃分。通過具體的實驗測試,本系統的通用性及高效性得到了驗證,并且該系統可方便地移植到不同的實際應用中。

引言

隨著多媒體技術以及通信技術的迅猛發展,高質量數字圖像的應用越來越廣泛,然而未經壓縮的數字圖像的數據量非常大,勢必會給圖像的存儲和傳輸都帶來很大的困難,因此對數字圖像的有效壓縮是不可或缺的。在現有圖像壓縮編碼技術中,靜態圖像壓縮編碼標準JPEG以其顯著的壓縮效率、較低的圖像質量損失以及較低的實現復雜度得到了廣泛應用,是常用的國際標準。

JPEG靜態圖像壓縮標準于1991年由聯合圖像專家組JPEG(Joint Picture Expert Group)制定[1]。發展至今,JPEG圖像壓縮系統在各大通用處理器平臺上的軟件實現早已成熟,但由于這些算法的實現需要大量系統資源(內存、浮點運算)的消耗,很難直接移植到資源有限的嵌入式平臺中。為了實現JPEG圖像壓縮在嵌入式平臺中的應用,不少學者對JPEG編碼算法進行了優化,并在ARM微控制器、高性能DSP中進行了實現[24]。由于圖像質量及其對處理實時性要求的不斷提高,一些學者提出了采用FPGA并行硬件來實現JPEG圖像壓縮算法的解決方案[5],且取得了不錯的效果。

若使用ARM微控制器進行開發,軟件方法的實現受限于指令的串行執行,處理速度不會太快,且存在計算性能不足等問題。而使用高性能DSP進行實現時,雖然DSP內部有專門的結構加速實現數字信號處理,但存在開發復雜、可移植性不強等問題,而且由于是串行指令執行系統,仍存在處理速度上的局限。針對單純使用FPGA進行開發時,雖然硬件并行計算的優勢能滿足圖像編碼算法處理性能上的需求,但在圖像數據的采集(如USB攝像頭)以及數據傳輸通信(如網絡傳輸)方面,相較嵌入式CPU而言,存在開發難度大、復雜度高、資源消耗多等問題,不利于系統通用平臺化實現。要實現完整通用的圖像壓縮系統,可以采用ARM和FPGA軟硬件協同設計的方式來實現整個系統平臺,ARM處理器完成數字圖像的采集以及壓縮后數據的傳輸,FPGA作為協處理器,通過高速并行計算完成JPEG編碼算法的硬件實現。

針對ARM和FPGA這種異構多核的協同開發,核間通信速率通常是系統設計的限制所在,但目前單芯片上集成ARM和FPGA的技術已經很成熟,如Xilinx公司2011年推出的Zynq7000系列芯片[6],片內高性能通信總線很好地解決了核間通信速率這一瓶頸。本文采用搭載有XC7Z020CLG484芯片的ZedBoard平臺完整地實現了JPEG圖像壓縮系統,在利用FPGA并行處理優勢加速實現JPEG編碼算法的同時,ARM部分便捷地實現了圖像數據的采集、簡單的預處理,以及壓縮后數據的傳輸等功能。

1系統整體實現結構

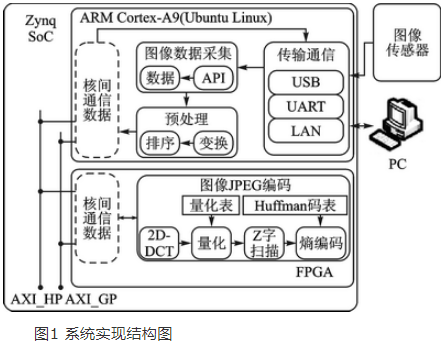

系統平臺按照處理流程主要分為3個部分:圖像數據獲取、圖像編碼處理以及壓縮后的數據傳輸。本系統的整體實現結構如圖1所示。

圖像數據獲取部分主要目的是采集需要壓縮處理的圖像數據,包括圖1中的傳輸通信模塊和圖像數據采集模塊。本系統平臺提供兩種實現方式:一種面向實際圖像傳輸應用,通過在嵌入式硬件平臺中直接連接數字圖像傳感器來獲取圖像數據進行處理;另一種則面向圖像處理算法的調試驗證,由PC機通過以太網或串口發送特定的圖像數據到嵌入式平臺中進行圖像處理算法的驗證。這兩種圖像數據采集方式均由ARM部分編寫相應的驅動程序進行實現。

圖像編碼處理部分是該系統平臺的核心,包括圖1中的預處理模塊和圖像JPEG編碼模塊。這部分是基于Baseline JPEG算法實現的[7],主要包括圖像的色彩空間變換、排序、二維離散余弦變換(2DDCT)、量化、Z字掃描和熵編碼等模塊,圖像經該算法處理后即可得到壓縮數據。該部分由ARM和FPGA協同處理實現。

壓縮后數據傳輸部分是指將壓縮后的數據由嵌入式硬件平臺通過圖1中的傳輸通信模塊發送至PC機端,完成圖像的解碼顯示。對于串口發送這一方案,由于傳輸速度慢,只適用于圖像處理算法的驗證,要實現PC機端圖像的實時顯示則需要通過以太網傳輸。該部分的具體實現在ARM端進行。

其中針對圖像數據獲取和壓縮后數據傳輸這兩部分在ARM端的軟件實現,本系統在Zynq7000 SoC的ARM CortexA9雙核中移植了Ubuntu Linux操作系統,其具備大量可利用的開源函數庫資源,極大地方便了圖像傳感器驅動和以太網通信的實現。

2 Baseline JPEG編碼單元的設計與實現

本系統是在ZedBoard平臺上實現的,圖像數據的采集由ARM端完成,要實現JPEG編碼算法在FPGA中的硬件加速,FPGA需要與ARM進行通信從而獲取到需要壓縮處理的圖像數據。系統中ARM與FPGA核間通信采用的是Zynq7000片內的高性能通信總線AXI_HP,通過DMA的形式進行數據傳輸,AXI_HP總線最高位寬為64位,理論通信帶寬最高可達1200 MB/s。

由于Baseline JPEG編碼是使用以DCT為基礎的順序編碼工作方式,在編碼過程中,先將原圖像分割成8×8的數據塊(如果是彩色圖像,需先進行色彩空間的變換),圖像子塊按照一定的掃描順序依次輸入,對每一個8×8尺寸圖像子塊使用二維離散余弦變換去除圖像數據在空間上的相關性,然后根據指定的量化表進行數據的量化處理,減少數據大小,再對數據進行Z字掃描,便于數據編碼,接著根據指定的熵編碼表進行編碼,減小數據編碼長度,最終得到壓縮圖像的編碼數據。為了充分發揮AXI_HP總線最高64 位傳輸位寬以及FPGA并行處理等特性,本模塊將簡單的圖像預處理部分在ARM部分進行實現,而2DDCT、量化、Z字掃描、熵編碼等部分則在FPGA部分進行硬件加速實現。

2.1ARM部分軟件的設計

圖像壓縮編碼部分在ARM端的軟件實現主要是完成圖像預處理的功能,具體包含色彩空間的變換以及圖像數據的排序兩個部分。

2.1.1色彩空間變換

JPEG是針對連續色調(灰度和彩色)靜止圖像壓縮編碼的標準,由彩色圖像傳感器獲取到的圖像通常是由RGB(即紅綠藍)三種顏色分量組成,彩色圖像進行JPEG壓縮前需要進行色彩空間的轉換,通常轉換為YCrCb空間,包含一個亮度分量和兩個色度分量,由灰度圖像傳感器獲取的灰度圖像只有單一亮度分量,不需要轉換。

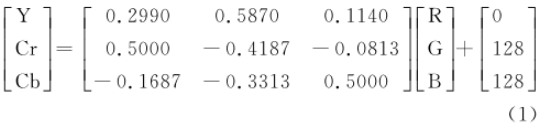

RGB與YCrCb空間轉換關系如下:

在進行2DDCT前,需要將圖像像素值轉換為有符號數,即將幅值減去128,所以使用式(1)進行色彩空間變換時,得到的每個分量值還需減去128以轉換為有符號數。這些轉換含有浮點運算,為提高處理效率,在ARM端軟件實現時可將各浮點運算的結果制成表格,進行色彩空間轉換時通過查表的方式實現,節省了浮點運算占用的處理時間。

彩色圖像的壓縮處理是將色彩空間變換后得到的Y、Cr、Cb三個分量按照灰度圖像(單一Y分量)的壓縮方法分別進行壓縮。本文中主要以Y分量(灰度圖像)的壓縮為例進行介紹,其他分量的處理方法類似。

2.1.2圖像數據排序

JPEG壓縮編碼是以8×8數據塊為基本單元進行編碼,一幅圖像中所有圖像子塊是以從左到右、自上往下的順序進行處理的。本系統在ARM端完成色彩空間的轉換得到亮度值后,先對圖像數據按照處理順序進行了重新排列,再通過64 位寬的AXI_HP總線將數據傳輸給FPGA端進行后續處理。通過這樣的設計,FPGA端獲取到重新排列后的數據后,便可以直接進行以8×8數據塊為基本單元的壓縮處理流水實現,無需涉及到圖像數據的存儲等待時間,可減少總體處理時間。

2.2FPGA部分軟件的設計

本系統中在FPGA部分主要是完成對預處理后數據的壓縮編碼,具體包含2DDCT、量化、Z字掃描以及熵編碼4個模塊。

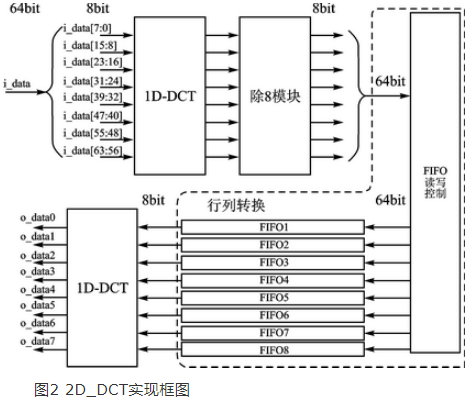

2.2.12DDCT

對于2DDCT(二維離散余弦變換)的實現,本文采用行列分解快速算法,先對8×8圖像子塊的所有行完成一維離散余弦變換(1DDCT),再對變換結果的每一列進行一維離散余弦變換,就可以得到2DDCT的結果。該部分具體實現框圖如圖2所示,針對AXI_HP總線最高64 位傳輸位寬的特性,即可實現8個像素的圖像數據并行輸入,其中行列處理的轉換是通過控制8個64位輸入、8位輸出FIFO的讀寫進行實現的。1DDCT模塊采用Leoffler DCT算法進行優化實現[8],大量減少了乘法器資源的消耗,其中涉及到的浮點小數乘法運算采用定點整數乘法進行替代。

2.2.2量化

量化過程就是將經過二維離散余弦變換后得到的頻域系數,根據重要性的不同,分別除以不同的量化步長,從而得到量化結果,具體實現框圖略——編者注。為了提高處理速度,采用乘法運算代替除法運算,本文中使用的量化步長是將JPEG標準推薦量化表的倒數乘以211后得到的,并存儲在ROM中,經過量化后,將計算結果右移11位即恢復為實際的量化結果。

2.2.3Z字掃描

經過量化處理后,每個8×8圖像子塊中將出現很多值為0的高頻分量,主要集中在8×8矩陣的右下角,使用Z字形掃描的方式將8×8的二維系數矩陣變成一維數據流(第一個為DC系數,其余63個為AC系數),這樣可以使0值分量集中,以便之后的數據編碼,具體實現框圖略——編者注。

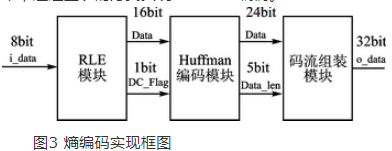

2.2.4熵編碼

為了減少圖像的編碼長度,要對Z字掃描后的DC系數和AC系數做基于統計特性的熵編碼,該部分主要是DC系數根據直流Huffman編碼表進行差分編碼,AC系數先進行行程長度編碼,再根據交流Huffman編碼表進行編碼,實現框圖如圖3所示。其中Huffman編碼模塊是將JPEG標準推薦的Huffman編碼表存儲在ROM中,通過查表的方式實現Huffman編碼。

3實驗及結果分析

本系統實驗平臺略——編者注,該實驗硬件平臺主要包括以下幾個部分:①Kinect傳感器,生成分辨率為640×480的數字圖像數據;

②搭載有XC7Z020CLG484芯片的ZedBoard開發板,實現JPEG圖像壓縮系統;

③無線路由器,連接ZedBoard與PC機,實現以太網通信。

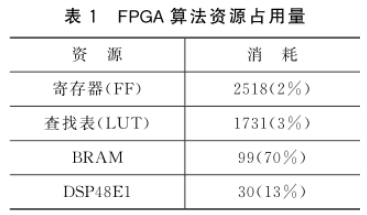

本實驗中,Zynq SoC平臺ARM部分移植了Ubuntu Linux操作系統,由OpenNI驅動程序獲取Kinect傳感器生成的圖像數據,進行色彩空間的變換得到亮度分量Y,重排序后通過AXI_HP總線傳輸給FPGA部分。FPGA部分讀取ARM端預處理后的圖像數據,然后進行圖像壓縮編碼。實現640×480像素灰度圖像壓縮編碼算法的FPGA資源占用量如表1所列,算法實現中涉及640×480尺寸數據的存儲,因此消耗了較多的BRAM資源。FPGA部分完成圖像壓縮編碼后,便將壓縮后的數據通過AXI_HP總線傳輸回ARM部分,最后通過以太網傳輸壓縮后圖像數據到PC端,進行實時解碼顯示。

經過實驗測試,ARM端CPU運行時鐘頻率為667 MHz,完成一幅圖像數據的采集、預處理等操作,需要耗時約14 ms;FPGA端運行時鐘頻率為100 MHz,完成ARM端預處理后數據的讀取、圖像壓縮編碼等操作,需要307 251個時鐘周期,耗時3.07 ms。由于不同復雜度的圖像壓縮后數據量不一樣,所以每幅圖像壓縮后數據傳輸回ARM端的時間也不一樣。如圖4所示的實驗測試圖樣,在具有大量圖像細節的情況下,本系統實現的壓縮比為13.81,經過FPGA算法壓縮完成后的數據傳輸回ARM需耗時0.03 ms,完成圖像壓縮處理的時間總消耗不超過17.5 ms。針對Kinect傳感器30 fps的幀率而言,該系統在一個圖像周期內足以完成圖像壓縮處理操作,具備良好的實時性。

圖4所示為隨機獲取兩幅圖像的實驗測試結果,測試結果表明,該系統在獲得較大壓縮比的同時,保留了原始圖片的關鍵信息,能滿足實際應用需求。

結語

本文主要介紹了一個基于Zynq SoC的JPEG圖像壓縮系統的實現過程。該系統按照處理流程劃分為圖像數據獲取、圖像編碼處理以及壓縮后數據傳輸3個部分。本文創新性的采用了ARM與FPGA軟硬件協同設計的方式對JPEG圖像壓縮系統進行了高效實現,充分結合了ARM與FPGA各自在開發上的特點,并采用Zynq片上高性能AXI_HP總線實現了ARM與FPGA核間高速通信。

上一篇:ARM嵌入式系統開發發送過程的實現

下一篇:基于AT91SAM9260 的ZigBee工業以太網網關設計

推薦閱讀

史海拾趣

S3C72N4

S3C72N4

京公網安備 11010802033920號

京公網安備 11010802033920號