幾乎所有的電子設計師和嵌入式系統開發人員都聽過現場可編程門陣列(FPGA)。對于實際的FPGA器件,設計人員和開發人員都知道它擁有可編程架構,能夠對其進行配置來而執行想要的功能,但他們的了解可能僅限于此。同樣,當涉及創建一個可以在FPGA上實現的設計時,他們可能聽過硬件描述語言(HDL)和寄存器轉換級電路(RTL)之類的術語,但可能并未充分理解它們的含義。

與Verilog或VHDL相似,HDL能讓FPGA設計人員描述設計意圖,正如軟件開發人員使用C或者C++等編程語言一樣。理解HDL的方式之一就是它可以用來描述同時發生的事物,這也是現實世界中硬件工作的方式。相比之下,軟件編程語言通常用于描述順序發生的事。

同時,RTL是常用于邏輯綜合引擎輸入的抽象級電路。該工具將RTL轉換到邏輯元件和互連網絡,然后在FPGA的可編程邏輯內實現。邏輯綜合引擎可以比作軟件開發者的編譯器,后者采用高級程序作為輸入,并將其轉換為由處理器執行的機器代碼。

FPGA的可編程結構可用于構建硬件加速器,以低功耗執行數據處理任務。可編程結構經過配置后可創建一個或多個更適合處理決策任務的軟核處理器,這些處理器還可以控制硬件加速器,包括向其提供數據并根據結果采取相應措施。

RISC-V就是這樣一種處理器,它是一種開源指令集架構(ISA),可以通過開源許可免費獲得。RISC-V開源硬件概念的創造者受到Linux開源軟件成功的啟發。RISC-V的一大優勢是在各類設計實現中都有出色的軟件兼容性,并且目前這些處理器的使用急劇增長。

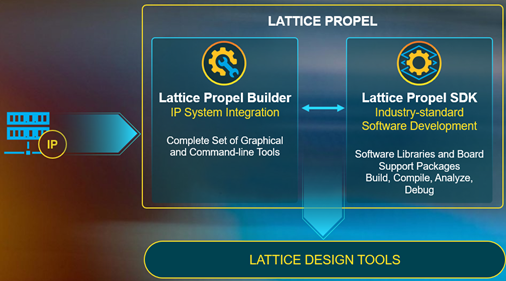

然而,對于想要使用這種處理器的非FPGA設計人員而言,問題在于他們缺乏有關FPGA設計語言、工具和流程的專業知識。為了解決這個問題,低功耗可編程FPGA的領先供應商萊迪思半導體開發了名為Lattice Propel?的工具,這是一款基于圖形用戶界面(GUI)的設計環境,任何用戶(無論是否具有FPGA專業知識)都能使用它以拖放的方式快速設計基于RISC-V處理器的系統。

Propel輸出的是RTL文件,可以發送到綜合引擎,生成可載入FPGA的配置文件。之后軟件開發人員可以在基于FPGA的RISC-V設計實現上運行他們的RISC-V可執行文件,正如在其他任何RISC-V處理器上運行一樣。萊迪思為其FPGA客戶免費提供RISC-V IP核。

基于FPGA的解決方案

數據處理要求有合適的計算引擎。開發者擁有諸多不同選擇,包括微處理器(MPU)、微控制器(MCU)、圖形處理器(GPU)、FPGA和SoC等器件。

MPU和MCU在執行決策任務時效率很高,但是在實現原始數據處理算法時,無論是處理時間還是功耗都不太理想。SoC能以最低的功耗實現最高性能,但缺點是開發起來價格昂貴、耗費資源且十分耗時,并且在此類芯片架構中實現的算法基本上都是固定無法更改的,而系統采用的協議和標準會不斷變化,因此會帶來很多問題。

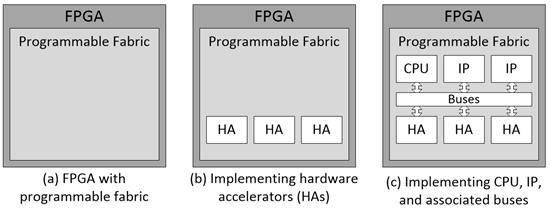

某些數據處理任務(包括許多AI/ML算法)非常適合并行處理。FPGA的可編程架構(圖1a)經配置可實現硬件加速器(HA)功能,以大規模并行方式執行任務(圖1b),從而顯著提高性能,同時降低功耗。

許多情況下還需要數據協處理功能,使用中央處理器(CPU)來強化硬件加速器,處理器可以執行高級決策和控制功能。不同于直接在芯片中實現的硬核CPU,FPGA的可編程架構能夠實現軟核CPU以及相關的總線結構(地址、數據、控制)和任何所需的外設IP功能(圖1c)。

圖1. 結構化總線的方法廣泛適用于各類應用,包括嵌入式視覺、安防和人工智能。

需要注意的是,根據FPGA器件和用戶的要求,額外的可編程邏輯功能和外圍通信功能(例如USB、MIPI、I2C、SPI、CAN和UART)可以通過硬核和/或軟核實現。文章篇幅有限此處不作贅述。

使用軟核CPU有諸多優點,包括能夠配置處理器的操作及許多可選功能,如動態內存訪問(DMA)控制器,從而對其精確調整,高效地滿足目標應用的要求。此外,如有需要,可以配置可編程結構實現其他外設IP功能。如在人工智能應用中,可以使用可編程邏輯資源來創建簡單的人工神經網絡,用于推理之類的任務。

RISC-V

如前所述,RISC-V是基于已有的精簡指令集計算機(RISC)原則的開源指令集架構,可通過開源許可獲得。此外,許多公司目前提供支持RISC-V的RISC-V硬核或開源操作系統,并且幾種主流的軟件工具鏈均支持該指令集。

RISC-V的模塊化設計包括基礎指令集和其他的擴展指令集。在行業、技術界和教育機構的共同努力下,兩者已得到長足的發展。基礎指令集規定了指令(及其編碼)、控制流、寄存器(及其大小)、存儲器和尋址、邏輯(即整數)操作以及輔助功能。僅基礎指令集就能實現具有全面軟件支持(包括通用編譯器)的通用計算機。

還可以通過可選拓展指令集實現額外功能,從而讓設計人員靈活選擇其應用所需的功能。RISC-V定義了許多擴展指令集,包括A(原子)、F(單精度浮點)、D(雙精度浮點)、Q(四精度浮點)和C(壓縮的16位指令以減少代碼尺寸,用于存儲空間有限的系統)。上述指令集均可靈活選擇。

圖2. 萊迪思是首個支持RISC-V的基于閃存和SRAM的FPGA供應商。

與作為專用處理器的硬核實現相比,基于FPGA的軟核RISC-V擁有的巨大優勢在于FPGA可重新配置的巨大潛力能夠滿足各種擴展需求。

萊迪思RISC-V軟核IP套件擁有32位RISC-V處理器核以及可選的定時器和可編程中斷控制器(PIC)子模塊。該CPU核支持RV32I指令集、外部中斷和符合JTAG IEEE 1149.1規范的調試。

定時器子模塊是一個64位實時計數器,它將實時寄存器與另一個寄存器進行比較以觸發定時器中斷。PIC子模塊最多將八個外部中斷輸入聚合為一個外部中斷。處理器核通過使用行業標準的32位AHB-L總線接口訪問子模塊寄存器。

萊迪思Propel

許多嵌入式系統的設計人員都對使用FPGA很感興趣,但是一想到要使用傳統的FPGA設計工具和HDL就望而卻步。為了解決這一問題,萊迪思Propel采用了基于圖形用戶界面(GUI)的設計環境,任何用戶(無論是否具有FPGA專業知識)都能使用其拖放的設計方式快速構建和配置基于RISC-V處理器的設計。

Propel輸出的是使用Verilog HDL語言的RTL文件,可以將其發送到綜合引擎,生成可載入FPGA的配置文件。該配置文件可用于萊迪思CrossLink?-NX(面向嵌入式視覺應用)、Certus?-NX(通用FPGA)以及MachXO3D?和Mach?-NX FPGA(安全系統控制)系列產品。FPGA配置完成后,軟件開發人員可以在基于FPGA的RISC-V設計實現上運行他們的RISC-V可執行文件,正如在其他任何RISC-V處理器上運行一樣。

Lattice Propel由兩個部分組成。首先是Propel Builder,它提供圖形化的拖放界面,讓用戶選擇IP模塊并將其連接在一起。這些IP模塊包括RISC-V處理器(帶有可選的定時器和中斷控制器)、AMBA總線結構、接口、存儲器、輸入/輸出(I/O)等。用戶還可以方便地在線升級現有IP模塊和獲得新的IP模塊 。

圖3. Propel界面直觀、易于使用、功能強大。

除了拖放IP實例化,Propel Builder還能自動進行引腳連接,通過向導配置和設置參數以及采用按構造逐步校正進行IP集成。

其次是萊迪思Propel SDK(軟件開發套件),可提供無縫的軟件開發環境。它擁有行業標準的集成開發環境(IDE)和工具鏈。SDK還為Propel Builder定義的系統提供軟件/硬件調試功能以及軟件庫和板級支持包(BSP)。

需要注意的重要一點是,Propel可以很好地對接下游工具,并且它也是一個獨立的程序,且其大小僅為0.5 GB,可以快速輕松地下載和安裝。同樣令人感興趣的是,Propel的所有命令都可以用Tcl編寫,從而提高了設計效率并將其快速集成到用戶自己的設計環境中。

圖4. 無論是簡單的“Hello World”應用還是復雜的嵌入式控制和數據處理系統,Propel都能讓用戶快速完成設計

對于硬件設計,Propel是那些需要FPGA優勢但缺乏FPGA硬件設計經驗的團隊的理想選擇。此外,如果團隊成員確實具有FPGA設計經驗,那么他們還可以根據需要對設計做更為精確的控制。對于軟件設計,Propel提供行業標準的C/C ++開發環境。軟件開發人員似乎更多地使用現成的微控制器。

設計人員可以使用Propel在CrossLink-NX、Certus-NX和Mach-NX FPGA中快速輕松地生成基于RISC-V軟軟核的處理器系統,從而提供復雜的視頻處理、系統控制和系統安全功能,其延遲遠遠低于通過外部獨立處理器實現的設計。

總結

除了擁有以低功耗執行高性能數據處理任務的邏輯功能和硬件加速器外,FPGA內部的可編程架構還可用于實現一個或多個更適合決策任務的軟核處理器,以及用于諸如硬件加速器之類的控制功能,包括向它們提供數據并根據結果采取措施。

RISC-V就是這樣一種處理器,它是一種開源指令集架構(ISA),可以通過開源許可免費獲得。萊迪思是首個支持RISC-V以及為其FPGA客戶免費提供RISC-V IP核的基于閃存和SRAM的FPGA供應商。

對于想要使用這種處理器的非FPGA設計人員而言,問題在于他們缺乏有關FPGA設計語言、工具和流程的專業知識。為了解決這個問題,萊迪思提供了Propel來簡化設計流程,讓開發人員能夠快速設計基于RISC-V處理器的系統。

上一篇:云上EDA實現的局限性都有什么?哪類設計適合上云

下一篇:UnitedSiC全新FET-Jet計算器,可迅速制定出設計決策

推薦閱讀

史海拾趣

HALO Electronics公司的發展故事

故事一:初創與早期技術突破

HALO Electronics,全稱HALO Electronics, Inc.,成立于1991年9月19日,總部位于美國德克薩斯州。公司自成立之初便專注于通信和功率磁性元件的設計與制造。在成立的早期,HALO便展現出了強大的技術創新能力。1993年,HALO推出了TnT?模塊,這是首個具有成本效益的10base2模塊,專為房地產敏感的薄網和背板應用設計,這一產品迅速在市場上獲得了認可。緊接著,1994年,HALO又開發了一種專利的SMD變壓器技術,為行業提供了更為強大的變壓器解決方案,進一步鞏固了其在磁性元件領域的地位。

故事二:與行業領先企業的合作

HALO Electronics的發展離不開與行業內領先企業的緊密合作。1995年,HALO與Maxim Integrated Products合作,共同開發了TGM-P3系列低成本PCMCIA變壓器,這些變壓器專為MAX253/845系列單片振蕩器/功率驅動器設計,用于小型低成本DC/DC轉換器。這一合作不僅提升了HALO產品的市場競爭力,也為其在高端應用領域的拓展奠定了堅實基礎。

故事三:創新產品的持續推出

HALO Electronics一直致力于創新產品的研發與推出。1997年,公司推出了Quatra?系列首個四端口T1/E1磁性模塊,這一產品是與Level One(Intel)共同開發的,提供了更高密度的T1/E1解決方案。隨后,在1998年,HALO又創造了Ultra?系列變壓器,這是當時最具成本效益和房地產效率的10/100base-TX變壓器,其SOIC16封裝成為了單端口快速以太網應用的行業標準。這些創新產品的推出,不斷推動著HALO在電子行業的領先地位。

故事四:安全與效率并重的產品開發

HALO Electronics在產品開發過程中始終注重安全與效率。1999年,公司宣布了業界首個UL認可的4.5KV隔離變壓器系列,這些變壓器專為需要高度安全的以太網應用設計,滿足了市場對高安全性產品的迫切需求。同年,HALO還推出了業界較小的雙端口T1/E1變壓器系列,進一步提升了產品的空間利用率和效率。這些舉措不僅彰顯了HALO在產品安全與效率方面的卓越追求,也為其贏得了更多客戶的信賴和支持。

故事五:全球化布局與市場份額的擴大

隨著業務的不斷發展,HALO Electronics逐漸開始了全球化布局。公司在全球范圍內建立了多個銷售辦事處和倉庫,包括加州圣克拉拉、內華達州拉斯維加斯、香港和新加坡等地。同時,HALO還在北美、歐洲和亞洲的主要地區設立了衛星辦公室,由區域經理負責開展工作。此外,HALO還在全球范圍內擁有眾多制造商代表和分銷商,形成了完善的銷售和服務網絡。這些舉措不僅提升了HALO的市場覆蓋率和服務能力,也為其在全球范圍內的市場份額擴大奠定了堅實基礎。如今,HALO已成為電子行業中備受矚目的磁性元件供應商之一。

在全球電子行業快速發展的背景下,DRS面臨著來自各方面的挑戰。為了應對這些挑戰,DRS不斷加強研發投入,提高產品質量和服務水平。同時,公司也積極拓展國際市場,尋求更多的合作機會。通過這些努力,DRS在全球電子行業中保持了領先地位,并為未來的發展奠定了堅實的基礎。

請注意,由于篇幅限制,以上故事均為概述性質,具體細節和背景信息可能有所省略。

在市場競爭日益激烈的情況下,品牌形象的塑造對于企業的發展至關重要。1992年,公司名稱變更為COSEL株式會社,這一變革不僅提升了公司的品牌形象,也展示了公司向更高目標邁進的決心。同時,公司還導入了V.I(視覺整合),通過統一的視覺形象傳達公司的品牌理念和價值觀。這些舉措使得Cosel公司在客戶心中留下了深刻的印象。

浙江東亞電子不僅在國內市場上取得了顯著成績,還積極開拓國際市場。公司已為多家世界五百強企業、上市公司提供服務,如華為、中興、通用電氣及西門子等。通過與這些國際知名企業的合作,公司不僅提升了自身品牌的影響力,還積累了豐富的國際市場經驗。

隨著電子行業的競爭日益激烈,Anachip公司意識到單憑自己的力量難以應對市場的快速變化。于是,公司開始積極尋求與其他企業的合作。通過與多家知名電子企業建立戰略合作關系,Anachip成功將自己的芯片技術應用于更多領域,進一步擴大了市場份額。同時,這種合作模式也促進了整個電子行業的共同發展。

自2001年正式進入中國市場以來,Beckhoff在中國的業務得到了迅速發展。公司先后在北京、上海、廣州、成都等地設立了分支機構,并在多個城市設立了辦事處。隨著中國市場的不斷擴大和需求的不斷增長,Beckhoff不斷推出適應中國市場的新產品和技術,為中國客戶提供更加便捷、高效的服務。

|

負載拉移(Load-Pull)原理在射頻功率放大器設計中的應用.pdf 近年來由於微波通訊技術的進步,及通訊頻寬與移動性越來越高的需求,使得無線區域網路(Wireless LAN)在人類日常生活中之重要性大幅提昇,進而帶動產學界紛紛投入此系統電路技術及產品之研發。… 查看全部問答∨ |

Ansoft SIwave v3 (電磁場全波分析): Ansoft 發布SIwave V3 ——增加了封裝/電路板的協同設計和EMI/EMC的動態連接技術 Ansoft公司發布了Ansoft SIwave 3.0,用于高性能PCB板和IC封裝的信號完整性和電源完整性分析的全波電磁場仿真器。新的版本 ...… 查看全部問答∨ |

|

單片機應用系統課程是目前電類專業的主干課之一,其操作性很強,對于院校學生,光靠課堂上的教學是遠不夠的,除了在課堂上要求學生掌握基本概念,了解單片機擴展接口電路的設計方法和設計編制程序的流程之外,只有通過課外大量的實際操作,才能掌握 ...… 查看全部問答∨ |

|

|

我買了一塊c8051f020DK的開發板,原來板上標配的液晶是不帶字庫的(控制芯片KS0108),然后我自己又去買了塊帶字庫的(控制芯片st7920),我接在了板上的引出腳上。今天調試的時候發現,進入調試環境后,直接就跳入了匯編界面,我切換到C程序界面發 ...… 查看全部問答∨ |

|

|

大蝦們幫幫忙啦 我在用LM3S1512做一個定時器紅外捕捉解碼的project 使用的是Rowley CrossStudio開發環境我按照數據手冊的介紹寫了如下面的相關代碼 問題是當我逐步執行代碼的時候 定時器初始化什么的都沒問題 而且程序不會 ...… 查看全部問答∨ |

- 非常見問題解答第233期:自動測試設備應用中PhotoMOS開關的替代方案

- 當AI加速落地,這企業級SSD新品不容錯過

- AMD 加碼 CPO 共封裝光學,收購硅光子初創團隊 Enosemi

- 意法半導體擴大在新加坡的“Lab-in-Fab”廠內實驗室合作項目, 推進壓電MEMS技術的開發應用

- 英偉達 2026 財年 Q1 營收 440.62 億美元,凈利潤同比增長 26%

- 新型傳感器系統問世:可在能見度極差環境探測200米外障礙物

- 顛覆iToF技術,安森美如何突破30米深度感知極限?

- 利用驗證框架 JAIST揭示開源自動駕駛系統的安全漏洞

- 現代汽車集團擬采用VR模擬器替代道路測試 提升未來車型的競爭力

- 研究人員開發光驅動致動器 可用于驅動水下機器人

EPA3756G-12.5

EPA3756G-12.5

京公網安備 11010802033920號

京公網安備 11010802033920號