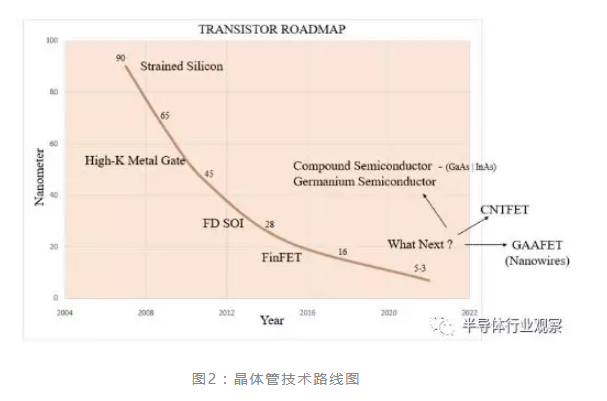

推動晶體管往5nm以下節點微縮是VLSI工業的關鍵問題之一,因為越變越小的晶體管帶來了各種各樣的挑戰,全世界也正在就這個問題進行一些深入研究以克服未來技術節點的挑戰。

在本文,我們回顧了包括如碳納米管FET,Gate-All-Around FET和化合物半導體在內的潛在晶體管結構和材料,他們被看做解決現有的硅FinFET晶體管在5nm以下節點縮放的問題。

半導體時代始于1960年,是伴隨著集成電路的發明而開啟的。在集成電路中,所有有源/無源元件及其互連都集成在單個硅晶圓上,這就使得它們在便攜性、功能性、功耗和性能方面具有領先的優勢。而在過去幾十年里,VLSI行業也在摩爾定律的“指導”下快速發展。所謂摩爾定律,是指集成在芯片上的晶體管數量大約每兩年增加一倍。

為了從縮小尺寸的晶體管獲得相應的收益,VLSI行業在不斷改進晶體管的結構、材料、制造技術以及設計IC的工具。到目前為止,晶體管所采用的各種技術包括了高K電介質,金屬柵極,應變硅(strained silicon),雙圖案化(double patterning),從多個側面控制通道,絕緣體上的硅(SOI)和更多技術。其中一些技術在《關于CMOS,SOI和FinFET技術的評論文章》中有討論過。

如今,物聯網,自動駕駛汽車,機器學習,人工智能和互聯網流量的需求呈指數增長,這將給晶體管帶來了縮小到現有7nm節點以下以獲得更高性能的驅動力。然而,縮小晶體管尺寸卻存在若干挑戰。

亞微米(Sub-Micron)技術的問題:

每次我們縮小晶體管尺寸時,都會生成一個新的技術節點。所以我們已經看到了如28nm,16nm等的晶體管尺寸。我們知道,縮小晶體管可以實現更快的開關、更高的密度、更低的功耗,更低的每晶體管成本以及跟多的其他增益。

基于CMOS(互補金屬氧化物半導體)的晶體管可以在28nm節點上運行良好。然而,如果我們將CMOS晶體管縮小到28nm以下,則短溝道效應變得不可控制。在該節點下,由drain-source電源產生的水平電場試圖控制通道。結果,柵極不能控制遠離它的漏電路徑。

16nm / 7nm晶體管技術:FinFet和FD-SOI:

VLSI工業已采用FinFET和SOI晶體管用于16nm和7nm節點,因為這兩種結構都能夠防止這些節點的漏電問題。這兩種結構的主要目標是最大化柵極到溝道(gate-to-channel)的電容并最大限度地減小漏極到溝道(drain-to-channel)的電容。在兩個晶體管結構中,引入溝道厚度縮放作為新的縮放參數。隨著溝道厚度減小,沒有路徑(path),因為它已經遠離了柵極區域離。因此,柵極對通道具有良好的控制,這就消除了短通道效應。

在絕緣體上硅(SOI)晶體管中,使用掩埋氧化物層,其將主體與圖1(a)中所示的襯底隔離。由于BOX層,漏—源(drain-source)寄生結電容減小,這帶來更快的切換。對SOI晶體管來說,它們面對的主要挑戰是難以在芯片上制造薄硅層。

圖1:a)FD-SOI結構b)FinFET結構和通道

FinFET,也稱為三柵極控制通道,如圖1(b)中的三個側面所示。我們可以看到,有一個薄的垂直“硅體”,看起來像是由柵極結構包裹的魚的Fin。通道的寬度幾乎是Fin高度的兩倍。因此,為了獲得更高的驅動強度,我們就使用了多Fin結構。FinFET的收益之一是帶來了更高的驅動電流需求。但FinFET面臨的主要挑戰是復雜的制造工藝。

5nm以下的挑戰:下一步是什么?

隨著表面粗糙度散射增加的,同時減小“硅體”厚度,這將會帶來較低的遷移率。這主要因為FinFET是3D結構,所以降低了散熱方面效率。此外,如果我們進一步縮小FinFET晶體管尺寸,比如低于7nm,則漏電問題再次出現。再加上如自加熱(self-heating)和閾值平坦化(threshold flattening)等諸多問題也會被考慮進來,這就推動我們去研究其他可能的晶體管結構,并用新的有效材料替換現有材料。

根據ITRS路線圖(國際半導體技術路線圖),下一代技術節點分別為5nm,3nm,2.5nm和1.5nm。在VLSI行業和學術界,也正在進行許多不同類型的研究和研究,以尋找滿足這些未來技術節點要求的潛在解決方案。在這里,我們討論一些有前景的解決方案,其中包括了碳納米管FET(carbon nanotube FET)、GAA晶體管結構和化合物半導體等用于未來節點的技術。

CNTFET - 碳納米管FET:

CNT(碳納米管)展示了一類新興的半導體材料,它是由卷起的單片碳原子組成以形成的管狀結構。CNTFET是一個場效應晶體管(FET),使用半導體CNT作為兩個金屬電極之間的溝道材料,這就形成了源極和漏極接觸。在這里,我們將討論碳納米管材料以及它如何在較低的技術節點下給FET帶來提升。

什么是碳納米管?

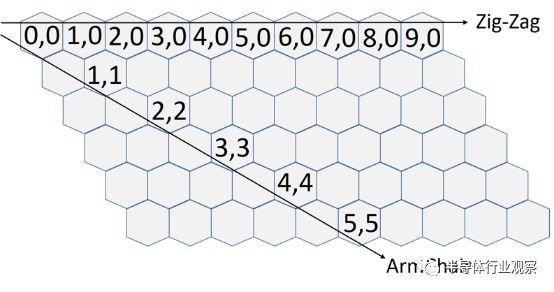

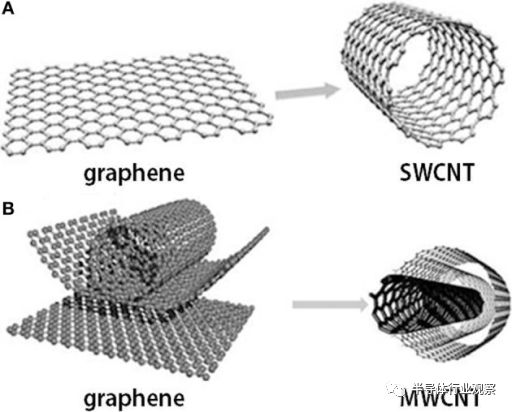

CNT是由碳制成的管狀材料,擁有可在納米尺度上測量的直徑。它們具有長而中空的結構,由一個原子厚的碳片形成,這個東西就被稱為“石墨烯”(Graphene)。碳納米管具有不同的結構、長度、厚度、螺旋度和層數。主要被分類為單壁碳納米管(Single Walled Carbon Nanotube :SWCNT)和多壁碳納米管(Multi-Walled Carbon Nanotube :MWCNT)。如所示圖3(a) ,可以看到,單壁碳納米管是由單層的石墨烯構成,而多壁碳納米則是由多個石墨烯層組成。

圖3:a)單壁和多壁CNT b)手性矢量表示

碳納米管的特性:

碳納米管在熱穩定性和物理穩定性方面具有優異的表現,如下所述:

1、金屬和半導體行為

CNT可以表現出金屬和半導體行為。這種行為變化取決于石墨烯片的卷繞方向,這被稱為手性矢量(chirality vector)。該向量由一對整數(n,m)表示,如圖3(b)所示。如果'n'等于'm',或者'n'和'm'的差值是三的整數倍,則CNT表現為金屬,否則它表現為半導體。

2、令人難以置信的流動性

因為SWCNT能夠表現為金屬或半導體,所以擁有對稱傳導(symmetric conduction)和承載大電流的能力,這就使得它們具有很強的電子應用潛力,由于沿CNT軸的低散射率,沿CNT長度的電子和空穴具有很高的電流密度。數據顯示,CNT可以承載大約10 A / nm^ 2的電流,而標準金屬線的載流能力僅為10 nA / nm^ 2。

3、出色的散熱性

熱管理是電子設備性能的重要參數。碳納米管(CNT)是眾所周知的納米材料,擁有出色的散熱性能。此外,與硅相比,它們對I-V特性的溫度升高影響較小。

晶體管應用中的CNT:CNFET

碳納米管的帶隙可以通過其手性(chirality)和直徑改變,因此可以使碳納米管表現得像半導體。半導體CNT可以是納米級晶體管器件溝道材料的有利候選者,因為它提供了遠超傳統硅MOSFET的許多優點。碳納米管傳導熱量類似于鉆石或藍寶石。此外,與硅基器件相比,它們的切換更可靠,功耗更低。

此外,CNFETS的跨導率(trans-conductance)比其對應物(counterpart)高四倍。CNT可與High-K材料集成,從而為通道提供良好的柵極控制。由于遷移率增加,CNFET的載流子速度是MOSFET的兩倍。在相同的晶體管尺寸下,N型和P型CNFET的載流子遷移率類似。但在CMOS中,因為遷移率值不同,PMOS(P型金屬氧化物半導體)晶體管尺寸大約是NMOS(N型金屬氧化物半導體)晶體管的2.5倍。

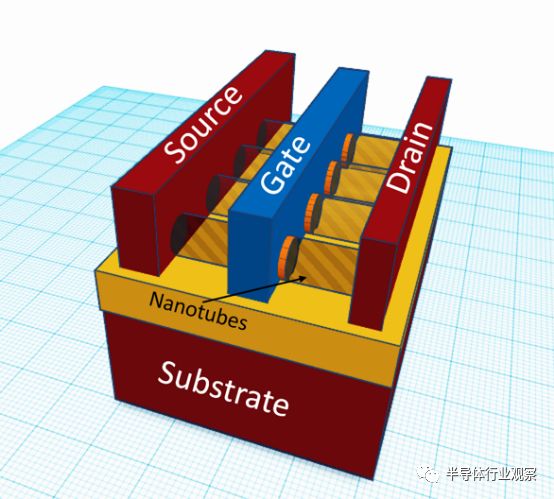

CNTFET的制造是一項非常具有挑戰性的任務,因為它需要精確和準確的方法。在這里我們討論頂部門控(Top-gated)的CNTFET制造方法。

該技術的第一步始于將碳納米管放置在氧化硅襯底上,然后分離各個管,使用先進的光刻來定義和圖案化源極和漏極觸點。然后通過改善觸點和CNT之間的連接來減小接觸電阻。通過蒸發(evaporation)技術在納米管上進行薄頂柵(top-gate)電介質(dielectric)的沉積(deposition)。最后,為了完成該過程,柵極接觸被沉積在柵極電介質上。

圖4:碳納米管FET的概念

CNTFET面臨的挑戰:

在商用CNFET技術的路線圖上,存在許多挑戰。他們中的大多數已經得到一定程度的解決,但其中也有一些尚未得到克服。在這里,我們將討論CNTFET的一些主要挑戰。

1、接觸電阻

對于任何先進的晶體管技術來說,晶體管尺寸減小而帶來的接觸電阻的增加是他們面對的主要性能問題。由于晶體管的按比例縮小,接觸電阻顯著增加,這就帶來晶體管性能下降。到目前為止減小器件觸點的尺寸帶來執行量(execution)大幅下降,這是硅和碳納米管晶體管技術面臨的挑戰。

2、碳納米管的合成

CNT的另一個挑戰是改變其手性(chirality),使其表現得像個半導體。合成的管(synthesized tubes)具有金屬和半導體的混合物。但是,由于只有半導體元件有資格成為晶體管,因此需要發明新的工程方法,在將金屬管與半導體管分離時獲得明顯更好的結果。

3、開發非光刻工藝,將數十億個這些納米管放置在芯片的特定位置上,這構成了極具挑戰性的任務。

目前,許多工程團隊正在對行業和大學中的CNTFET器件及其邏輯應用進行研究。在2015年,一家領先的半導體公司的研究人員成功地使用“緊密接觸方案”(close-bonded contact scheme)將金屬觸點與納米管結合起來。他們通過在管的末端放置金屬接觸并使它們與碳反應形成不同的化合物來實現這一點。這項技術幫助他們將觸點縮小到10納米以下而不影響性能。

Gate all around FET:GAAFET

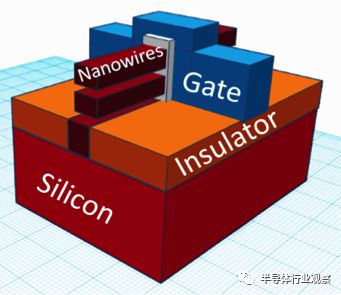

未來的潛在晶體管結構之一是GAAFET(Gate all around FET)。Gate-all-around FET是FinFET的擴展版本。在GAAFET中,柵極材料從四個方向圍繞溝道區域。在簡單的結構中,作為溝道的硅納米線被柵極結構“包圍”。垂直堆疊的多個水平納米線結構被證明非常適合于提高每個限定區域的電流。圖5中展示出了多個垂直堆疊的gate-all-around硅納米線的概念。

圖5:垂直堆疊的納米線GAAFET

除硅材料外,還可以使用一些其他材料,如InGaAs,鍺納米線,借助這些材料能獲得更好的移動性。

在復雜的柵極制造,納米線和接觸方面,GAAFET存在許多障礙。其中一個具有挑戰性的工藝是從硅層制造納米線,因為它需要一種新的蝕刻工藝方法。

最近,位于魯汶的研發公司聲稱,他們在直徑為10納米以下的納米線上使用GAAFET在通道上實現了出色的靜電控制。去年,一家領先的半導體公司推出了一款5nm芯片,該芯片采用堆疊納米線GAAFET技術,在50mm^2芯片上集成了300億個晶體管。據稱,與10nm節點相比,該芯片性能提高了40%,在相同性能下功耗降低了70%。

化合物半導體

繼續晶體管微縮的另一種有希望的方法是選擇表現出更高載流子遷移率的新型材料,而擁有來自III、V族成分的化合物半導體與硅相比,明顯擁有更高的遷移率。其中一些化合物半導體實例是銦鎵砷(InGaAs),砷化鎵(GaAs)和砷化銦(InAs)。根據各種研究,化合物半導體與FinFET和GAAFET的集成在更小的節點處表現出優異的性能。

化合物半導體的主要問題是硅和III-V半導體之間的大的晶格(lattice)失配,導致晶體管溝道的缺陷。有一家公司開發了一種含有V形溝槽的FinFET進入硅襯底。這些溝槽充滿銦鎵砷并形成晶體管的鰭片。溝槽底部填充磷化銦以減少漏電流。利用這種溝槽結構,已經觀察到缺陷在溝槽壁處終止,從而能夠降低溝道中的缺陷。

結論

從22nm節點到7nm節點,FinFET已被證明是成功的,并且它還可以繼續縮小到另一個節點。但我們也應該看到,除此之外,還存在各種挑戰,如自加熱,遷移率降低,閾值平坦等。

我們已經討論了碳納米管的優異運動特性,散熱性,高載流能力,這將為替代現有硅技術提供了有前景的解決方案。

隨著水平納米線的堆疊打開“第四柵極”,Gate-all-around晶體管結構也是替換FinFET垂直Fin結構以獲得良好靜電特性的良好候選者。

雖然目前尚不清楚技術路線圖中的下一步是什么。但是可以肯定的是,在未來的晶體管技術中,必須改變現有的材料,結構,EUV(極紫外)光刻工藝和封裝,才能繼續延續摩爾定律。

上一篇:邊緣計算、7納米礦機將在未來2年成為新的搖錢樹

下一篇:解析:中國FAB廠與大硅片項目的布局規劃

推薦閱讀

史海拾趣

為了進一步擴大市場份額,維峰電子積極開拓國內外市場。公司通過與國內外知名企業的合作,成功進入了多個領域,包括工業控制、汽車和新能源等。特別是新能源領域,維峰電子憑借其在電子連接器方面的技術優勢,成功開發出多款適用于新能源領域的產品,受到了市場的廣泛認可。

在20世紀90年代初,G-Mag Usa公司由一群電子工程師創立,專注于研發高性能的半導體芯片。當時,市場上對于小型化、低功耗的芯片需求日益增長。G-Mag通過不斷的技術創新,成功研發出了一種新型低功耗處理器,該處理器在保持高性能的同時,能耗降低了30%。這一技術突破迅速吸引了眾多智能手機制造商的注意,G-Mag因此迅速崛起,成為半導體行業的佼佼者。隨著智能手機市場的爆發式增長,G-Mag的芯片出貨量也隨之飆升,公司規模迅速擴大。

芯邦科技自成立以來,一直致力于半導體技術的研發與創新。在指紋識別領域,芯邦于2018年推出了業界首款超低成本、超低功耗的指紋識別控制芯片,該芯片集成了指紋傳感器、算法處理器、藍牙、主控和flash等模塊,為指紋識別技術在非手機領域的廣泛應用提供了強有力的技術支撐。這一創新不僅展示了芯邦在半導體設計領域的實力,也為其在指紋識別市場贏得了先機。

隨著市場的不斷擴大和客戶需求的多樣化,Colibrys逐漸發展成為一站式制造商。公司提供從設計到制造以及最終測試的完整供應鏈服務,確保客戶能夠安全、高效地采購到一流性能的MEMS產品。這種服務模式不僅提高了公司的市場競爭力,也贏得了客戶的廣泛認可和信賴。

Ettinger與英國著名汽車品牌Bentley建立了長期合作伙伴關系。作為Bentley汽車皮件配飾和皮具產品的指定供應商,Ettinger為Bentley提供了高品質的皮具產品,進一步提升了品牌的知名度和影響力。這種合作伙伴關系的建立,也為Ettinger帶來了更多的商業機會和發展空間。

隨著公司業務的不斷發展,Echelon開始積極拓展全球市場。公司通過在海外設立分支機構、與當地企業合作等方式,將LonWorks技術和能源管理服務方案推廣至全球各地。同時,Echelon還積極參與國際能源管理標準的制定和推廣工作,提升了公司在國際市場的知名度和影響力。

|

隨著時代的發展,獲取信息的速度已經成為制約互聯網發展的重要因素。 但一直以來,由于電信企業的競爭和限制,國內南北兩地網民一直飽受 “網絡瓶頸”問題的困擾。對此,許多企業機構只能采取大量增設基礎 設施,購買帶寬或某些技術措施來進行解 ...… 查看全部問答∨ |

|

|

不知道有沒有人發過了 不過還是拿來分享一下! 內文提示: 速度取決于算法 同樣的事情,方法不一樣,效果也不一樣。 比如,汽車引擎,可以讓你的速度超越馬車,卻無法超越音速; 渦輪引擎,可以輕松超越音障,卻無法飛出地球; 如果有火 ...… 查看全部問答∨ |

|

|

FPGA程序設計者,最后是全同步設計,這樣所有程序都在主時鐘同一個節拍下工作,系統時序分析和統計都有參照,程序穩定不容易出問題。 但是很多初學者由于對這個問題不了解或研究不深入經常寫下面的程序: LIBRARY ieee;use ieee.std_logic_1164.a ...… 查看全部問答∨ |

|

|

懂得西門子SAB-C165-LM芯片的編程環境及編程器的高手快進來看看!~~~ 小弟公司的一臺設備的一塊電路板壞了,檢修人員說是主芯片程序丟了,主芯片為西門子公司的SAB-C165-LM,我們也不知道到底是不是程序丟了,所以想自己測試一下,原程序都有(c的),但是因為以前沒用過這種芯片,不知道它的編譯環境和程序是怎么下載 ...… 查看全部問答∨ |

|

- 點評《讓世界更安全——TI Hercules開發實戰手冊》,精彩好禮等你拿!

- 【EEWORLD第三十一屆】2011年10月社區明星人物揭曉!

- 幫忙他人,成就自我——EEWORLD問答榜(10期)

- 與英飛凌一起,探索Matter奧義!

- 參加MSP430F5529培訓,長知識、免費送、超低團、搶樓得!

- 有獎國產芯直播:先楫800MHz RISC-V MCU高能秀,豈止控4只伺服電機,干貨多多

- “慧眼”識PCIe——閱讀《PCIe要了解的十件事》和泰克OPEN-DAY的培訓資料 抽獎、分享贏好禮!

- 沁恒CH579M-R1開發板免費測評,豐富外設等你體驗

- 最后一天!Beetle ESP32-C3免費測評,趕緊上車

- 關注有禮 | 泰克中端示波器增“重”計劃

LTC3526LBEDC-PBF

LTC3526LBEDC-PBF

京公網安備 11010802033920號

京公網安備 11010802033920號