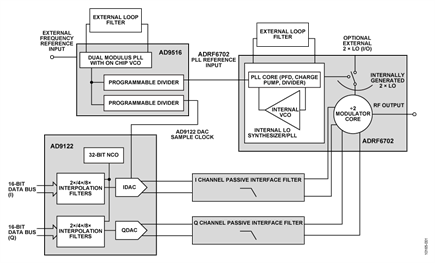

將 ADRF6702IQ調制器和 AD9122 16位雙通道1.2 GSPS TxDAC結合使用可滿足現代高水平QAM或OFDM無線發射器(如圖1所示)的動態范圍要求。該電路的動態范圍出色,足以同時支持ZIF(零中頻/基帶)和CIF(最高200 MHz至300MHz的復合中頻)。AD9122可選最高8×插值和一個32位NCO,以獲得超精細中頻靈敏度。

發射器的整體性能和直接組成信號鏈的組件動態范圍息息相關。在使用DAC和IQ調制器的混合信號發射器中,這類組件的本底噪聲和失真特性決定了信號鏈的整體動態范圍。但是,DAC的本底噪聲也可能由于采樣時鐘抖動而變得更嚴重,而且IQ調制器性能取決于其本地振蕩器(LO)的噪聲和雜散特性。因此采樣時鐘和LO發生采用高性能組件是高性能發射器的關鍵所在。

此外,在PCB板上盡量靠近DAC和調制器的位置產生這些信號并使用一個外部參考源也可大大簡化設計。單獨產生采用時鐘和LO(LO絕大多數為數GHz信號)并且與DAC和IQ調制器保持一定距離,要求十分謹慎地處理PCB布局。哪怕最細微的布局錯誤都可能會引起這些關鍵信號發生耦合,并降低整體信號鏈性能。

信號鏈性能也很大程度上取決于DAC/ IQ調制器接口濾波器。為優化性能,建議在仔細分析所需系統規格后再設計這款無源濾波器。

ADRF6702包括一個板載分數PLL用于LO生成,這樣只需一個低頻參考(一般低于100 MHz)即可合成IQ調制器LO。在AD9516時鐘發生器內使用PLL允許一個參考同時為ADRF6702產生DAC采樣時鐘和PLL參考。

圖1中的電路使用AD9516-0構建而成,也可選用AD9516系列的其他產品,具體取決于所需的內部VCO頻率。

?

配有內部LO合成器、合成器IQ調制器接口的ADRF6702 IQ調制器

ADRF6702 IQ調制器是一種具有多種特性的獨特器件。除出色的動態范圍外,它還包括一個分數-N PLL,允許編程設置低于25 kHz的離散LO頻率步進,同時仍保持足夠小的整體頻率倍增以避免從參考到合成器輸出的相位噪聲激增。

ADRF6702的另一特點是IQ調制器的2分頻架構。傳統IQ調制器接受1倍所需LO的LO輸入頻率。在內部,分布式RC網絡從單LO頻率輸入產生所需的同相和正交LO信號。因為這屬于無源RC網絡,所以實現正交調制精度的帶寬有限。而且,為獲得出色的正交精度,外部LQ應保持頻譜純凈。這種傳統LO調制器架構在LO上所產生的諧波可能會降低整體調制精度。為此,當使用PLL合成器來產生IQ調制器所需的LO信號時,往往需要在IQ調制器LO輸入端配置一個窄過渡帶的帶通或低通濾波器。

在ADRF6702的2分頻LO架構中,內部使用一個簡單數字分頻器在較寬頻帶上產生近乎完美的正交。PLL合成器內部產生2倍LO,所以不必在PCB周圍分配,并且因為2倍LO架構只受LO信號沿而非頻率成分影響,故在合成器和IQ調制器LO之間無需配置任何濾波器。有關LO諧波對1× IQ調制器和LO濾波器設計影響的詳情,請參見 電路筆記CN-0134。

?

信號采樣至RF、總本底雜散

基帶信號通過數個步進一直到達RF發射頻率。該信號在離散(采樣)域開始并由DAC合成至模擬域。這一步導致DAC產生圖像和失真積。如圖2所示,沒有失真的理想DAC將會產生多幅基帶信號圖像,隨后必須在調制前加以濾波。使用諸如AD9122系列的插值濾波器可以抑制大多數圖像能量,但仍需要在DAC和調制器之間配置一個模擬接口濾波器。不過需要權衡取舍DAC插值和模擬濾波器的階數。DAC插值速率越高,所需的模擬濾波器階數越低,反之亦然。作為示例,圖3顯示了使用4倍插值時的DAC輸出頻率波形。

?

多種RF雜散分量并存

由于調制積、失真積和LO頻率的整數倍,該信號鏈可能會大幅增加雜散分量。如果我們考慮所有討論過的潛在雜散根源,雜散成分包括:

(j × LO_freq) + (k × DAC_sample_rate) +

(l × DAC_NCO_freq) + (m × DAC_input_IF)

其中j、k、I和m均為正無窮大和負無窮大之間的整數。

DAC/調制器無源接口濾波器

在DAC和IQ調制器之間的模擬接口是縮減整體雜散頻譜的關鍵。在DAC和IQ調制器之間的接口濾波器設計必須考慮多方面性能。

?

DAC_MOD接口濾波器拓撲

圖5所示為一種典型拓撲,它針對100 Ω差分輸入和輸出阻抗產生5階最平坦的巴特沃茲響應。實際響應如圖6所示。該濾波器在源阻抗和負載處使用4.6 pF電容。

這個數量級的電容(<20 pF)代表具有高截止頻率的濾波器。在使用這類較小電容值時寄生電容可能對頻率響應有顯著影響。

?

?

DAC和失真相關雜散分量

本來使用DAC插值濾波器就可以減少調制器輸入端的雜散成分,因此也可以降低RF輸出端的雜散成分。但是,仍可能會存在明顯的雜散成分。圖7顯示在下列條件下IQ調制器的RF輸出頻譜。

FLO = 1940 MHz

DAC 輸入數據速率 = 300 MSPS

DAC 插值 = 4×

DAC 頻率 = 150 MHz

DAC 輸入IF頻率 = 8 MHz

注意,最強的雜散分量(不含2098 MHz基頻)為2400 MHz DAC時鐘分量的2倍。這可能由于DAC輸出的共模和差模分量包含某些來自DAC時鐘的頻譜。IQ調制器輸入的共模抑制可消除大部分此類信號,但它仍包含大量能量。接下來的2062 MHz 和2242 MHz兩個最高雜散也似乎和DAC時鐘雜散相關。2242 MHz的雜散可以輕松表示成2 × (DAC時鐘– DAC基頻 ) = 2400 ? 158。2062 MHz的雜散沒有這么明顯,但差不多是(3 × LO) ? (3 × DAC clock) ? 158 = 5820 ? 3600 ? 158。如果上述分析無誤,并且可以在IQ調制器輸入端抑制DAC時鐘的共模分量,那么應該能夠大幅降低雜散。

?

如圖8所示,應用差分巴特沃茲濾波器可以大幅降低雜散水平。最強的雜散仍位于2062 MHz、2242 MHz,而2× DAC時鐘雜散則位于2400 MHz處。所有三種雜散分量均已大幅降低。

?

改變接口濾波器的拓撲通常可以提高DAC/IQ調制器接口的共模抑制性能。在圖9中,從濾波器輸入兩側和濾波器輸出兩側到接地,共模電容(9.0 pF)取代了輸入和輸出4.7 pF電容。這不會改變整體差分濾波器模式響應,但會影響此板的RF整體雜散成分。在2062 MHz和2242 MHz處的上述諧波降低至數dB,同時2× DAC時鐘分量約降低15dB,接近本底噪聲。

此處所示的拓撲和結果可能因布局而異,所以設計人員最好先進行濾波器布局實驗,特別要注意混用差模和共模電容可以實現最低的整體本底雜散。

?

合成器路徑和PLL相位噪聲

如圖1所示,此電路使用一個外部參考,為ADRF6702的PLL產生AD9122 DAC采樣時鐘和參考時鐘。AD9516是確保靈活性的關鍵。AD9516內置一個PLL和集成VCO。它還包含若干輸出,支持差分LVPECL、LVDS或單端CMOS編程,且每個輸出路徑均具有獨立的分頻器設置。在該電路中,其中一個輸出路徑用于DAC時鐘,而另一路輸出則用于ADRF6702分數-N PLL的參考輸入。

在ADRF6702中使用分數PLL有兩個好處。第一,分數PLL允許超精細地調諧輸出LO。例如,在輸入頻率為38.4 MHz、ADRF6702編程MOD值為1536時,LO可按25 kHz增量編程設置。第二,參考頻率不必等于LO頻率/分頻比,而且還可以高很多,使分頻比降低。因為輸出相位噪聲和參考相位雜散乘以分頻比成函數關系,這意味著RF下本身具有低相位噪聲。

合成器系統的一大關鍵指標是個別PLL和分頻器所疊加的相位噪聲量。圖10所示為頻譜分析儀在進行測量時的本底噪聲(綠線)、參考發生器相位噪聲(紅線)以及RF頻率為1961 MHz,LO為1940 MHz時的輸出相位噪聲(黃線)。在AD9516和ADRF6702中使用PLL組合確實可以明顯產生更高的近載波相位噪聲(偏移載波低于500 kHz),但不會明顯增加系統的寬帶噪聲。AD9516和ADRF6702內VCO的環路濾波器在測量電路內均設為約100 kHz帶寬。可通過降低這些環路濾波器的帶寬來減少近載波相位噪聲。請仔細查閱系統規格,再決定給定系統可忍受的近載波相位噪聲。

?

解決方案框圖

!注意:請使用瀏覽器自帶下載,迅雷等下載軟件可能無法下載到有效資源。

| 器件 | 類型 | 描述 | 數據手冊 |

|---|---|---|---|

| AD9516-3 | 時鐘發生器 | 14路輸出時鐘發生器,集成2.0 GHz VCO | 點擊下載 |

| ad9516-0 | 時鐘發生器 | 14路輸出時鐘發生器,集成2.8 GHz VCO | 點擊下載 |

| AD9516-1 | 時鐘發生器 | 14路輸出時鐘發生器,集成2.5 GHz VCO | 點擊下載 |

| AD9122 | 標準高速數模轉換器 | 雙通道、16位、1200 MSPS、TxDAC+?數模轉換器 | 點擊下載 |

| ADRF6702 | 集成LO的IQ解調器 | 1200MHz至2400 MHz正交調制器,采用1550MHz至2150 MHz小數N分頻PLL和集成式VCO | 點擊下載 |

| AD9516-2 | 時鐘發生器 | 14路輸出時鐘發生器,集成2.2 GHz VCO | 點擊下載 |

| AD9516-4 | 時鐘發生器 | 14路輸出時鐘發生器,集成1.6 GHz VCO | 點擊下載 |

歡迎加入EEWorld參考設計群,也許能碰到搞同一個設計的小伙伴,群聊設計經驗和難點。 入群方式:微信搜索“helloeeworld”或者掃描二維碼,備注:參考設計,即可被拉入群。 另外,如您在下載此設計遇到問題,也可以微信添加“helloeeworld”及時溝通。

EEWorld Datasheet 技術支持