Virtex-7 HT采用賽靈思的堆疊硅片互聯(lián)技術(shù),可提供多達(dá)16個(gè)28 Gbps收發(fā)器和72個(gè)13.1 Gbps收發(fā)器,也是唯一能滿足關(guān)鍵Nx100G和400G線路卡應(yīng)用功能要求的單芯片解決方案。擁有100G變速機(jī)制、以太網(wǎng) MAC、OTN 和Interlaken IP等。

其他FPGA集成的28 Gbps通道數(shù)僅為H580T 的四分之一...[點(diǎn)擊查看]

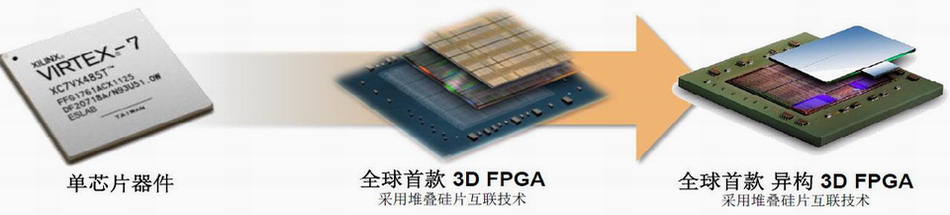

賽靈思堆疊硅片互聯(lián)技術(shù)的異構(gòu)3D FPGA是什么?

H580T是業(yè)界首個(gè)集成FPGA芯片與收發(fā)器的產(chǎn)品...[點(diǎn)擊查看]

Virtex-7 H580T FPGA 主要支持哪些常見應(yīng)用?...[點(diǎn)擊查看]

Virtex-7 HT產(chǎn)品優(yōu)勢(shì)及設(shè)計(jì)亮點(diǎn)

隨著信息與通信技術(shù)進(jìn)入高速發(fā)展期,通信產(chǎn)業(yè)正在經(jīng)歷著一場(chǎng)巨大的變革。而通信帶寬的需求增長(zhǎng)速度,已經(jīng)快于摩爾定律所預(yù)測(cè)的集成電路的增速。如何有效升級(jí)網(wǎng)絡(luò)、如何應(yīng)對(duì)數(shù)據(jù)用量的幾何級(jí)增長(zhǎng),這對(duì)通信產(chǎn)業(yè)而言至關(guān)重要。[詳細(xì)]

業(yè)界首款異構(gòu)3D FPGA,賽靈思Virtex-7 H580T 28G收發(fā)器性能演示

Virtex-7 H580T是賽靈思All Programmable產(chǎn)品中的一員,是采用賽靈思的SSI技術(shù),多達(dá)16個(gè)28Gbps收發(fā)器和72個(gè)13.1Gbps收發(fā)器,可提供業(yè)界最高帶寬的FPGA,也是業(yè)界目前唯一能滿足關(guān)鍵Nx 100G和400G線路卡應(yīng)用要求的單芯片解決方案。[詳細(xì)]

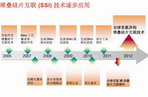

賽靈思堆疊硅片SSI技術(shù)演進(jìn)時(shí)間表

2006年開始開發(fā)堆疊硅片技術(shù)-2007年90nm工藝集成和模塊開發(fā)并完成初期可靠性評(píng)估-2008年完成90nm測(cè)試流程、設(shè)計(jì)實(shí)現(xiàn)和供應(yīng)鏈驗(yàn)證-2009完成65nm測(cè)試流程-2010完成28nm測(cè)試流程-2011完成設(shè)計(jì)工具,全球首款3D堆疊硅片互聯(lián)器件-2012全球首款異構(gòu)3D堆疊硅片互聯(lián)器件。

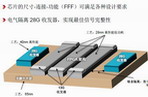

異構(gòu)帶來的優(yōu)勢(shì)

1.實(shí)現(xiàn)最大FPGA帶寬,串行連接能力達(dá)2.78Tb/s 2.芯片的尺寸-連接-功能(FFF)可滿足各種設(shè)計(jì)要求 3.電氣隔離 28G 收發(fā)器,實(shí)現(xiàn)最佳信號(hào)完整性。其中FPGA采用28nm制程,收發(fā)器采用40nm制程。無(wú)源中介層采用65nm制程。通過數(shù)字和模擬分離,實(shí)現(xiàn)最低噪聲和抖動(dòng)。

解決 Nx100G 應(yīng)用的空間、功耗及成本問題

CFP2較CFP寬度減半、功耗減半、系統(tǒng)成本更低,不過CFP2需要收發(fā)器規(guī)格為25G~28G。用Virtex HT可以取代原有的100G OTN 線路卡,并且支持CFP2光學(xué)模塊。需要將芯片從五個(gè)減少到一個(gè),功耗和成本均降低 30%,為背板提供可編程功能和靈活性,比ASSP的解決方案早一年多時(shí)間面市。

突破性可編程系統(tǒng)集成能力

HT系列最多擁有16個(gè)供系統(tǒng)集成使用的 28G 收發(fā)器、72個(gè)13G收發(fā)器,可支持400G MAC直接連接到 CFP2 模塊,可實(shí)現(xiàn)最佳信號(hào)完整性,有助于降低成本并加快設(shè)計(jì)收斂。