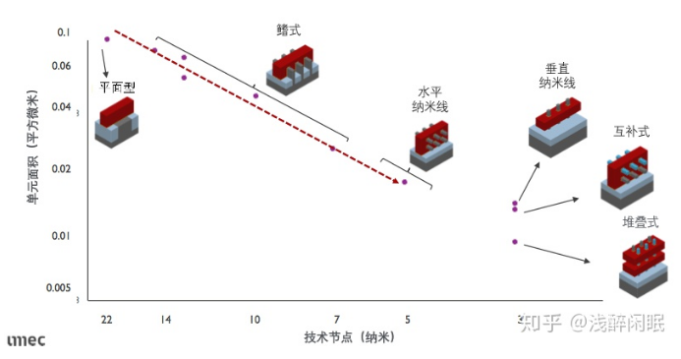

半導體技術發展史的本質就是晶體管尺寸的縮小史。從上世紀七十年代的10微米節點開始,遵循著摩爾定律一步一步走到了今天的5納米。在這一過程中,每當摩爾定律遭遇困境,總會有新的技術及時出現并引領著摩爾定律繼續前行。自22納米節點上被英特爾首次采用,鰭式場效應晶體管(FinFET)在過去的十年里成了成為了半導體器件的主流結構。然而到了5納米節點之后,鰭式結構已經很難滿足晶體管所需的靜電控制。其漏電現象在尺寸進一步縮小的情況下急劇惡化。因此,半導體行業急切需要一個新的解決方案在未來節點中替代鰭式晶體管結構。

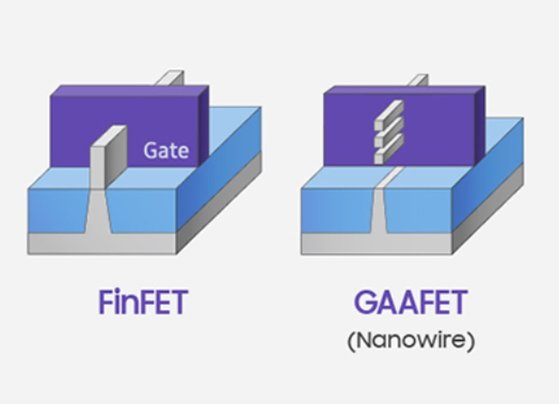

盡管各種新型晶體管方案不斷地被提出,然而工業界真正青睞的是能夠允許他們繼續使用現有設備以及技術成果的方案。正是基于這一原因,全環繞柵極晶體管(Gate-All-Around FET)被廣泛認為是鰭式結構的下一代接任者。在2019年的三星晶圓制造論壇(Samsung Foundry Forum)上,三星明確表示將會在3納米節點放棄鰭式結構,轉向全環繞柵極技術。在剛剛過去的臺積電第26屆技術研討會上,臺積電也正式宣布將在2納米節點引入全環繞柵極技術。目前英特爾仍然受困于7納米技術難產,尚未給出具體的計劃何時引入全環繞柵極技術。但英特爾的首席技術官麥克邁克· 梅伯里博士也在今年的國際VLSI會議上稱希望英特爾能在五年之內實現全環繞柵極晶體管的量產。那么這樣一個備受各大半導體廠商青睞的晶體管結構究竟是什么樣的呢?

平面型晶體管到鰭式結構的轉變

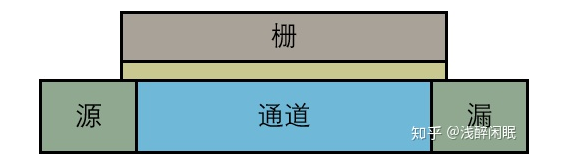

要搞清全環繞柵極技術,我們首先要從場效應晶體管(Field Effect Transistor)說起。所謂的晶體管,是指一種等效于水龍頭作用的電子器件。水龍頭可以用來控制水流的大小以及開關,與之類似晶體管的作用是控制電流的大小與開關。這里面另外一個關鍵詞是場效應,指的是這種對電流的控制是通過施加一個電場來實現的。如下圖所示的晶體管結構中,我們可以 通過對柵極施加一個電壓從而在通道內部產生一個電場。這個電場的大小可以被用來調節源極和漏記之間電流的大小。也由此可見,決定場效應晶體管效率的一個重要因素就是柵極對通道的控制能力。

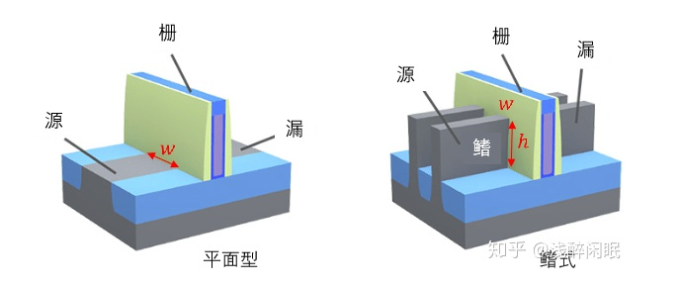

根據電阻的定義 ,我們可以簡單估算出源極到漏極之間電阻的大小是和柵極的長度成正比的。柵極越小,在同樣的電壓下能實現的電流也越大。這是決定晶體管性能的一個關鍵參數,也因此早期的技術節點往往是根據柵極的長度來命名的。所謂的10微米節點,指的就是柵極的長度最小為10微米。自從引入鰭式晶體管結構之后,技術節點中的數字僅僅是一個營銷代號,已經不再和晶體管的任何尺寸直接對應。

上圖中另外一個值得注意的地方是通道的長度并不等于柵極的長度。這是因為源極和漏極是通過離子注入(ion-implantation)實現的。在離子注入的過程中,會有離子擴散到柵極下方,形成所謂的擴散層。擴散層的存在,導致了在32納米節點之后,柵極長度無法進一步縮小(避免漏極和源極之間直接短路)。英特爾也因此在之后的22納米節點引入了鰭式晶體管。

從平面型晶體管過渡到鰭式晶體管,柵極對通道內電場的控制能力大幅提升。原先柵極與通道的接觸面積僅僅是由通道的寬度 決定的,而在鰭式晶體管中則是由 決定。更大的接觸面積導致了通道內電流傳輸的橫截面積更大,因而對應的電阻更小電流更高。

鰭式晶體管除了實現對通道更好的控制,另一個重要改進是允許柵極的長度進一步縮小。在平面型晶體管中,源極和漏極的生產是通過離子注入實現的。而在鰭式晶體管中,源極和漏極的則是在柵極做好之后直接在鰭上外延生長(Source-Drain Epitaxy)。此時由于柵極的阻斷,不會出現擴散層,也因此不會有短溝效應的問題。

下圖是英特爾在22納米節點首次引入鰭式晶體管時給出的掃描電子顯微鏡照片。從圖中我們可以看到,每一個單元都包含著兩組鰭,每組內部各三個。在另外一個方向上,更高的線則是柵線。鰭式晶體管的尺寸縮小的一個重要衡量參數就是鰭線(Fin Line)和柵線(Gate Line)的重復周期。其中鰭線的周期是半導體器件中所有結構中最小的周期,而柵線的周期對整個晶體管的性能有決定性的影響。在22納米節點,鰭線和柵線的周期分別為60,90納米。而到了5納米節點,鰭線和柵線的周期僅為27,54納米。

5納米之后,鰭式晶體管將會面臨一系列的問題。首先隨著柵線之間的間距進一步減小,很難再像之前那樣在一個單元內填充多個鰭線。而如果只做一個鰭線的話,生產工藝又很難保證不同器件之間性能一致。因為控制多個鰭線的平均尺寸要遠比控制單個鰭線的尺寸容易得多。其次也是更為致命的問題是,隨著柵線之間的間距進一步減小,鰭式晶體管的靜電問題急速加劇并直接制約晶體管性能的進一步提升。這里所說的靜電問題是指鰭式晶體管本身的結構帶來的一系列寄生電容以及電阻的問題。例如柵極與柵極之間的寄生電容,柵極與通道之間的寄生電容,柵極與金屬電極之間的寄生電容,以及源極與漏極之間的寄生電阻等問題。IMEC之前的模擬表明,當柵線之間的間距縮小至40納米之后,鰭式晶體管的性能將會趨于飽和。因此,在5納米之后,工業界迫切需要一個新的結構來替代鰭式晶體管結構,這就帶來了全環繞柵極晶體管。

全環繞柵極晶體管

前文中我們提到,工業界迫切需要一個新的晶體管結構來需要滿足以下幾個需求:

1. 新的結構所需的生產工藝應該與鰭式晶體管相似,可以繼續使用現有的設備以及技術成果;

2. 新的結構應實現對通道更好的控制,例如柵極與通道之前的接觸面積更大;

3. 新的結構帶來的寄生電容和電阻問題應得到顯著改善;

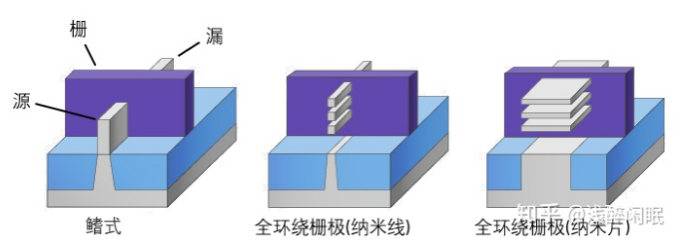

全環繞柵極晶體管的出現滿足了以上所有需求,從而允許摩爾定律在5納米之后進一步前進。首先其生產工藝與鰭式晶體管相似,關鍵工藝步驟幾乎一樣(這點我們會在之后的文章中進一步講解)。其次,全環繞柵極晶體管實現了柵極對通道之間的四面環繞,接觸面積由 提升到了 。最后由于源極與漏極之間的通道橫截面積顯著縮小,對應的寄生電容顯著降低,而寄生電阻顯著增大。

全環繞柵極晶體管的結構如下圖所示,根據源極與漏極之間通道的長寬比不同,分為納米線結構(中圖)以及納米片結構(右圖)兩種。在早期的研發中,包括IMEC和IBM等機構的早期工藝均采用的是納米線結構。這是因為較高的長寬比很難控制納米線與納米線之間的刻蝕與薄膜生長。隨著工藝的逐漸進步,在即將到來的2納米與3納米節點,臺積電三星等眾多廠商將會采用納米片結構來實現更大的接觸面積。而在納米片之后,工業界可能會重新回到納米線,因為納米線可以允許更小間距以及更大的表面積/體積比。

全環繞柵極之后晶體管的發展

根據當前的估計,水平方向上的全環繞柵極晶體管足以維持柵線的周期從54納米縮減到30~40納米左右(2~3代節點)。在此之后晶體管的發展,則充滿了挑戰與不確定性。在當前已知的幾種備選方案中,垂直納米線結構將會把納米線調整為垂直方向;互補式結構將會把N型晶體管和P型晶體管沿著垂直方向進行堆疊;而堆疊式結構則會把多個柵極在垂直方向上經行堆疊。這些新型的結構理論上均會表現出比水平納米線/片更加優越的性能,但是他們也需要更為先進的工藝水平才能實現商業化生產。從目前的信息來看,互補式結構最有可能是全環繞柵極晶體管之后的選擇。但至于未來究竟會走向何種結構,我們將拭目以待!

如何生產3納米以下全環繞柵極(Gate-All-Around)晶體管?

在前面我們探討了工業界是如何從平面型晶體管過度到鰭式,再過度到全環繞柵極晶體管的。我們提到工業界青睞全環繞柵極晶體管的一個重要原因是這種新的結構所需的生產工藝與鰭式晶體管非常相似,可以繼續使用現有的設備以及技術成果。那么全環繞柵極晶體管究竟是如何生產出來的呢?在本期文章中,我們將會詳細介紹其生產工藝。在10納米以下的先進制程中,生產一顆芯片通常需要幾千道工序,因此我們沒法詳細地介紹每一步工藝。這里我們將重點放在那些和鰭式晶體管不同的步驟進行討論。

超晶格外延生長(Superlattice Epitaxy)

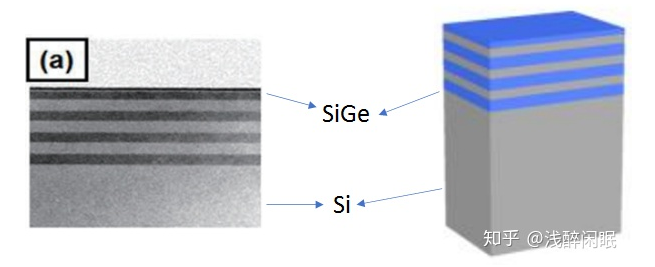

全環繞柵極晶體管的生產從硅(Si)片基底開始,第一步在Si上外延生長出三個Si-SiGe超晶格結構。這一步在鰭式晶體管的生產工藝中是不需要的。如上圖所示,左圖中淺色的薄膜以及右圖中灰色的薄膜為Si,而深色及藍色的薄膜則為SiGe。超晶格結構中的每一層厚度均在10納米以下,最終生產出的厚度會直接決定納米片通道的高度以及靜電性能。

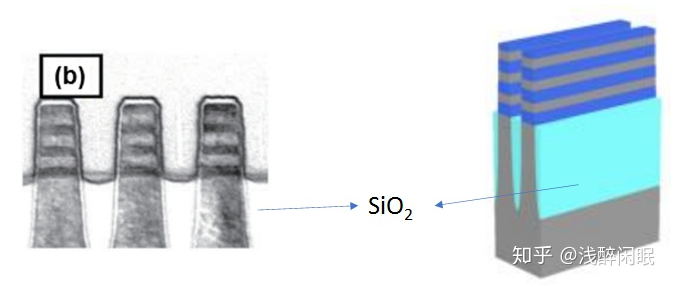

鰭式結構成型(Fin Formation)

在這一步中,我們通過光刻把前一步外延生產的超晶格薄膜做成一個一個周期分布的鰭。上圖中新出現的淺藍色材料是SiO2, 它的作用是隔開相鄰的兩個晶體管(鰭),因此也被稱作淺溝隔絕(STI Shallow Trench Isolation)。這一步工藝最早是從250納米節點開始引入的,在鰭式晶體管中也有完全一樣的生產步驟。通常鰭的周期是芯片所有結構中最小的周期,在5納米制程中相鄰的兩個鰭間距已經低至30納米,是通過自對齊四重曝光實現的(SAQP Self-Aligned Quadruple Patterning)。預計從3納米開始,這一步將使用EUV單次曝光實現。

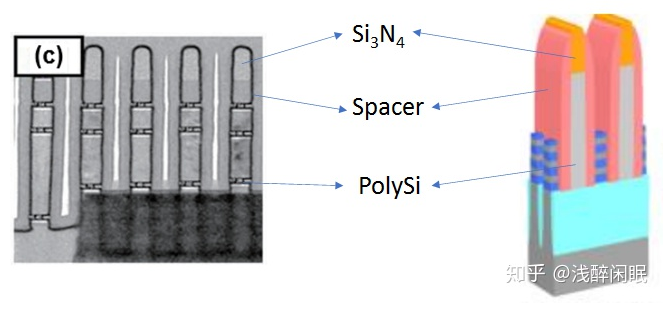

柵極成型(Gate Formation)

在這一步中,我們在與之前的鰭線相垂直的方向上做出周期分布的柵極。柵極所使用的材料是多晶硅(PolySi),柵極的上面附著的是氮化硅(Si3N4),在光刻中起到硬掩膜(Hard Mask)的作用。為了保護柵極避免其與源極漏極短路,柵極表面還會有一層隔離層(Spacer),隔離層的材料通常是氧化硅或者氮化硅。從目前的模擬來看,柵極的周期無法做到40納米以內,因此自對齊雙重曝光即可實現柵極的成型。預計在即將到來的3納米制程中,這一步將繼續使用193納米沉浸式光刻機進行光刻。

內隔離層成型(Inner Spacer Formation)

這一步的工藝實際包含三步。首先我們需要把柵極之間鰭全部清理干凈,清理出來的空間將來會用來生長源極和漏極。這也是為什么我們說柵極之間的間距很難做到40納米以下,因為40納米以下很難再有足夠的空間生長源極和漏極。然后我們將暴露在表面的SiGe材料刻蝕進去,這一步將是全環繞柵極晶體管生產中非常關鍵的一步,刻蝕的程度將直接決定晶體管中有效柵極的大小。最后在刻蝕過的SiGe表面生長內隔離層,與外部的隔離層類似,內隔離層的作用也是防止柵極與之后形成的源極漏極短路。

源極漏極的外延生長(Source Drain Epitaxy)

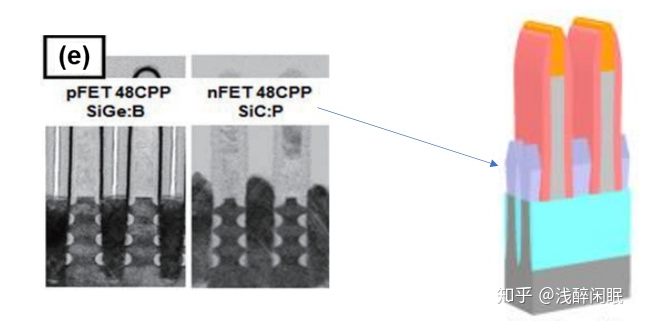

在成功的長出內隔離層保護柵極之后,這一步我們便可以在Si表面外延生長出源極和漏極。如果是P型晶體管,那么源極漏極的材料是硼摻雜的SiGe (SiGe: B)。如果是N型晶體管,那么源極漏極的材料則是磷摻雜的SiC (SiC: P)。這一步的工藝和鰭式晶體管的工藝也是一致的。然而值得注意的是,外延生產會給晶體管的通道施加很大的應變,這種應變對于晶體管的電學性能是非常有利的。但是在3納米以下的節點,全環繞柵極晶體管的通道是僅僅幾納米厚的薄片,且相鄰的薄片之間的距離也只有幾納米,這種應變可能會導致晶體管的嚴重變形。

通道釋放(Channel Release)

通道釋放可以說是全環繞柵極晶體管生產中非常華麗的一步。在經過幾百道工序之后,終于在這一步,我們通過選擇性的刻蝕把通道釋放到半空中,形成三個半懸空的納米線/納米片。而之前形成的柵極完全被清理掉了,也因此我們往往稱之前的柵極為虛設柵極(Dummy Gate)。在之后的工藝中,我們將會重新在納米線/納米片的表面生長出具備高介電常數的絕緣層以及金屬柵極(HKMG High-K Metal Gate)。

通道釋放也是我們這篇文章介紹的最后一步,之后的生產工藝與鰭式晶體管生產工藝幾乎是完全一致的,感興趣的朋友可以自行了解一下鰭式晶體管的后續工藝。

參考文獻:

1.Diebold, Alain C., Andy Antonelli, and Nick Keller. "Perspective: Optical measurement of feature dimensions and shapes by scatterometry." APL Materials 6.5 (2018): 058201.

2.Loubet, N., et al. "Stacked nanosheet gate-all-around transistor to enable scaling beyond FinFET." 2017 Symposium on VLSI Technology. IEEE, 2017.本文中所有的結構示意圖均來自于Nanometrics, Inc.(參考文獻1)。因Nanometrics本身不做任何工藝生產,推測所展示的示意圖是參考IMEC的工藝而來的。電子顯微鏡圖均來自GlobalFoundries和IBM的工藝流程(參考文獻2)。標題圖片來源于Samsung。

上一篇:聯手美國限制技術出口,日本在華為傷口上又撒了把鹽

下一篇:中國信息技術兩大短板:一硬一軟,RISC-V是一大機遇

推薦閱讀

史海拾趣

Federal Custom Cable公司成立于XXXX年,由幾位具有豐富電纜制造經驗的工程師創立。公司創立之初,就專注于為客戶提供定制化的電纜解決方案。他們深入了解不同行業對電纜的特殊需求,通過技術創新和工藝改進,生產出符合客戶要求的電纜產品。這種對定制化需求的精準把握,使Federal Custom Cable在競爭激烈的電纜市場中脫穎而出。

在半導體領域,技術創新是企業持續發展的關鍵。谷峰公司深知這一點,不斷加大研發投入,致力于新技術的研發與應用。其中,SGT(Super Junction Technology)技術的成功研發,是谷峰發展歷程中的一個重要里程碑。SGT技術以其低內阻、高效率的特點,成為高頻應用的理想選擇,極大地提升了谷峰產品的市場競爭力。此外,谷峰還推出了多款高性能的碳化硅MOSFET產品,進一步鞏固了其在功率半導體領域的領先地位。

ABI Electronics公司深知研發實力是企業發展的核心競爭力。因此,公司不斷加大對研發的投入,引進了一批高素質的研發人才,建立了完善的研發體系。通過與高校、科研機構等合作,ABI不斷吸收新的技術和知識,推動產品的升級換代,保持了在行業內的技術領先地位。

隨著技術的不斷成熟和市場的逐步認可,Astro Tool Corp公司開始積極拓展海外市場。通過與國際知名電子制造商建立合作伙伴關系,公司成功將產品打入國際市場。同時,公司還積極參與國際行業展會和交流活動,不斷提升品牌知名度和影響力。這些努力不僅為公司帶來了更多的訂單和合作伙伴,也進一步鞏固了其在全球電子制造工具市場的地位。

進入電子領域后,ELNA迅速在電子元件領域取得了突破。公司憑借其在材料科學和制造工藝方面的專長,成功開發出了一系列高性能的電子元件產品。這些產品廣泛應用于通信、計算機、消費電子等領域,為ELNA贏得了廣泛的客戶群。

為了保持技術領先,ELNA不斷投入研發資源,加強技術創新。公司積極引進國際先進的生產設備和檢測手段,提升產品品質和可靠性。同時,ELNA還加強了與國內外科研機構和高校的合作,共同推動電子元件技術的發展。

作為一家有社會責任感的企業,Fenfa Electronics Ltd公司始終關注環境保護和社會公益。公司積極推動綠色生產和可持續發展戰略,致力于減少生產過程中的能耗和排放。同時,Fenfa還積極參與各種社會公益活動,為當地社區和弱勢群體提供幫助和支持。這些舉措不僅提升了公司的社會形象,也為公司的可持續發展注入了新的動力。

|

本帖最后由 jameswangsynnex 于 2015-3-3 19:59 編輯 據iSuppli公司,消費電子(CE)產業正在進入連接無處不在的新時代,刺激裝備高帶寬無線視頻接口解決方案的視頻導向CE設備蓬勃發展。 iSuppli公司預測,2014年具有高帶寬無線視頻接口的支持視 ...… 查看全部問答∨ |

#include <msp430x24x.h> typedef unsigned char uchar; typedef unsigned int uint; uchar NUM_LED[16]={0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8, 0x80,0x90}; uint tt,shi,fen,i,miao=0; void delay(void) { ...… 查看全部問答∨ |

|

初學,不太明白,這兩個是一樣的嗎? 另外,刷rom說的解鎖radio,這個radio是什么?是誰提供的?我看用pb定制的時候,沒有radio組件。 … 查看全部問答∨ |

|

|

我是學國際經濟與貿易的的,以前沒學過電子,由于工作中的需要,想了解CCL和FR-4方面的知識,請問在網上哪里能夠找到這方面的知識啊?另外有哪些書或資料有講解啊? 我是學國際經濟與貿易的的,以前沒學過電子,由于工作中的需要,想了解CCL和FR-4方面的知識,請問在網上哪里能夠找到這方面的知識啊?另外有哪些書或資料有講解啊?… 查看全部問答∨ |

如果從工程師和研究生的專業方向來看,電子信息專業的方向大概有1)數字電子線路方向。從事單片機(8位的8051系列、32位的ARM系列等等)、FPGA(CPLD)、數字邏輯電路、微機接口(串口、并口、USB、PCI)的開發,更高的要求會寫驅動程序、會 ...… 查看全部問答∨ |

|

中國銀行的口令牌,到期時間是10/31/11,也就是今天,我一時去不了開辦地重新領一個,我想著應該是到夜里24點以前還有效吧,沒著急,想著下午再用網銀,可是現在一看,口令牌已經不顯示口令了(不是壞了,還顯示其它字符),大家說說這有道理么? ...… 查看全部問答∨ |

最近在做FPGA的項目,經常有人問我,FPGA的功耗多大,額定電流多少。我在datasheet上沒有看到啊。 FPGA的電壓不是很多種么,請問有知道的朋友么… 查看全部問答∨ |

DM74AS652WM

DM74AS652WM

京公網安備 11010802033920號

京公網安備 11010802033920號