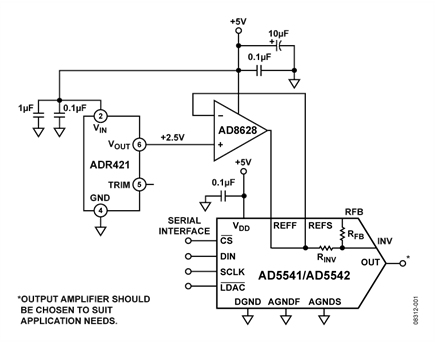

本電路利用電壓輸出DACAD5542 、基準電壓源ADR421BRZ以及用作基準電壓緩沖的自穩零運算放大器AD8628 ,可實現精密數據轉換。AD8628基準電壓緩沖可提供以前只有昂貴的自穩零或斬波穩定放大器才具有的特性優勢。這些零漂移放大器采用ADI公司的電路拓撲結構,將低成本與高精度、低噪聲特性融于一體。無需外部電容,而且與大多數斬波穩定放大器相關的數字開關噪聲大大降低,因此這種放大器是基準電壓緩沖的最佳選擇。

本電路可實現精密、低功耗、電壓輸出數模轉換。AD5542有兩種工作模式:緩沖模式和非緩沖模式。何種工作模式最佳由具體應用及其建立時間、輸入阻抗、噪聲等要求而定。可以根據直流精度或快速建立時間要求來選擇輸出緩沖放大器。如果要求DAC驅動60 kΩ以下的負載,則需要輸出緩沖。DAC的輸出阻抗恒定,且與數字碼無關,但為了將增益誤差降至最小,輸出放大器的輸入阻抗應盡可能高。輸出放大器還應具有1 MHz或更高的3 dB帶寬。輸出放大器給系統增加了另一個時間常數,因此會延長最終輸出的建立時間。

放大器的3 dB帶寬越高,則DAC與放大器組合的有效建立時間越快。電路中的所有器件均可采用+5 V單電源供電。基準電壓源ADR421的輸入電壓范圍為4.5 V至18 V。

?

本電路采用電壓輸出DAC AD5542,提供16位、高精度性能。AD5541/AD5542的DAC架構為分段R-2R電壓模式DAC。采用這種配置,輸出阻抗與數字碼無關,而基準電壓源的輸入阻抗則與數字碼高度相關。因此,基準電壓緩沖的選擇對于碼相關基準電流的處理非常重要,如果DAC基準電壓緩沖不充分,可能會導致線性誤差。選擇配合精密電壓輸出DAC使用的基準電壓緩沖時,運算放大器的失調電壓、失調誤差溫度系數和噪聲均是重要的選擇標準。基準電壓電路中的失調誤差會引起DAC輸出端產生增益誤差。本電路采用零漂移、單電源、軌到軌輸入/輸出運算放大器AD8628,其失調電壓為1μV,漂移低于0.005μV/°C,噪聲為0.5μV峰峰值(0.1 Hz至10 Hz),因而適合需要盡可能減少誤差源的應用。輸出電壓與基準電壓相關,如下式所示:

![]()

其中D為載入DAC寄存器的十進制數字字,N為DAC的分辨率。

對于2.5 V基準電壓,上述公式可簡化為下式:

![]()

因此,中間電平碼對應的VOUT 為1.25 V,滿量程碼對應的VOUT為2.5 V。

LSB大小為2.5 V/65,536 = 38.1 μV。

有一個普遍的誤解認為自穩零放大器不可靠,因為內部開關動作會導致交調項,并使不需要的諧波未經濾除便進入到輸出。以前的自穩零放大器采用自穩零或斬波穩定技術,傳統的自穩零技術使自穩零頻率時的噪聲能量較低,但由于自穩零頻帶中混疊寬帶噪聲,因此會造成低頻噪聲較高。斬波技術使低頻噪聲較低,但斬波頻率時的噪聲能量較大。AD8628系列采用已獲專利的乒乓式配置,同時使用自穩零和斬波技術,可在斬波和自穩零頻率獲得較低的低頻噪聲以及較低的能量,從而使大部分應用的信噪比達到最高,且不需要額外濾波。內部斬波頻率相對較高(15 kHz),因此在儀器儀表和過程控制應用中,可簡化對濾波器的有效、無噪聲、寬帶寬要求。

測量結果顯示:在高精度、高性能系統中將AD8628用作基準電壓緩沖,可以實現高精度、低噪聲以及最低高頻交調失真(折合到輸出端)性能。

積分非線性(INL)誤差指實際DAC傳遞函數與理想傳遞函數的偏差,用LSB表示。差分非線性(DNL)誤差指實際步進大小與1 LSB的理想值之間的差異。圖1所示電路在16位分辨率時的INL誤差為±1 LSB,DNL誤差為±1 LSB。圖2和圖3顯示了該電路的INL和DNL性能。

?

?

測得的失調誤差和增益誤差分別為10 μV和170 μV。±5 LSB的增益誤差和±1 LSB的零碼誤差均在38 μV額定誤差范圍(2.5 V基準電壓、環境溫度)內。

圖4顯示該電路的0.1 Hz至10 Hz噪聲圖。DAC的輸出VOUT與0.1 Hz至10 Hz帶寬濾波器的輸入端相連,濾波器之后接一個放大器,其增益為10,000。用一個示波器捕捉電壓噪聲,觀察到非常低的峰峰值電壓57 mV(相對于DAC輸出為5.7 μV)。

?

圖5顯示利用頻譜分析儀得到的DAC輸出,掃頻范圍為100 Hz至100 kHz。沒有觀察到明顯的交調失真(IMD)項,表明將AD8628等自穩零放大器用作基準電壓緩沖是極佳選擇。

?

在任何注重精度的電路中,精心考慮電源和電路板上的接地回路布局有助于達成目標。包含該電路的印刷電路板(PCB)應具有單獨的模擬和數字部分。如果該電路所在系統中有其它器件要求AGND至DGND連接,則只能在一個點上進行連接。該接地點應盡可能靠近AD5542。AD5542的電源應使用10 μF和0.1 μF電容進行旁路。這些電容應盡可能靠近該器件,0.1 μF電容最好正對著該器件。10 μF電容為鉭珠型電容。0.1 μF電容必須具有低有效串聯電阻(ESR)和低有效串聯電感(ESL),普通陶瓷型電容通常具有這些特性。針對內部邏輯開關引起的瞬態電流所導致的高頻,該0.1 μF電容可提供低阻抗接地路徑。電源走線應盡可能寬,以提供低阻抗路徑,并減小電源線路上的突波效應。時鐘和其它快速開關數字信號應通過數字地屏蔽起來,使之不受電路板的其它器件影響。

本電路必須構建在具有較大面積接地層的多層電路板上。為實現最佳性能,必須采用適當的布局、接地和去耦技術(請參考教程MT-031——“實現數據轉換器的接地并解開AGND和DGND的迷團”,以及教程MT-101——“去耦技術”)。

解決方案框圖

| 器件 | 類型 | 描述 | 數據手冊 |

|---|---|---|---|

| AD5541 | 單通道電壓輸出數模轉換器 | 2.7 V至5.5 V、串行輸入、電壓輸出、16位DAC | 點擊下載 |

| AD8628 | 低輸入偏置電流放大器 ( | 零漂移、單電源RRIO運算放大器 | 點擊下載 |

| ADR421 | 串聯基準電壓 | 超精密、低噪聲、2.500 V XFET?基準電壓源 | 點擊下載 |

| AD5542 | 單通道電壓輸出數模轉換器 | 2.7 V至5.5 V、串行輸入、電壓輸出、16位DAC | 點擊下載 |

歡迎加入EEWorld參考設計群,也許能碰到搞同一個設計的小伙伴,群聊設計經驗和難點。 入群方式:微信搜索“helloeeworld”或者掃描二維碼,備注:參考設計,即可被拉入群。 另外,如您在下載此設計遇到問題,也可以微信添加“helloeeworld”及時溝通。

EEWorld Datasheet 技術支持